为什么你的智能门锁过不了CE认证?ESP32射频设计三大盲区

合规不是贴标:从电磁兼容到密钥管理的生死线

2026年欧洲市场已有17款国产智能门锁因CE认证失败被下架,据欧盟NOTIFIED BODY统计数据显示,其中89%的案例与射频设计缺陷直接相关。这背后反映的共性问题是开发者低估了ESP32在复杂电磁环境下的合规复杂度。从工程实践来看,这绝对不是简单「加个屏蔽罩」就能解决的技术挑战。

核心结论:射频合规成本占硬件BOM 12%~25%

| 失败原因 | 典型成本追加项 | 解决方案周期 | 关键验证指标 | 测试设备要求 |

|---|---|---|---|---|

| 辐射超标(30MHz~1GHz) | 金属屏蔽罩+滤波电路 | 2~4周 | 3m法测试≤-10dB裕量 | 3m电波暗室+EMI接收机 |

| 信道干扰(868MHz) | 软件跳频算法+硬件SAW滤波器 | 3~5周 | LBT响应时间<300ms | 无线综测仪CMW500 |

| 密钥存储不合规 | 安全芯片(如ATECC608A) | 1~2周 | 抗侧信道攻击通过FIPS140-2认证 | 逻辑分析仪+差分探针 |

注:成本测算基于10000台量产规模,实验室费用未计入BOM

三大技术雷区与工程化验证方案

1. 你以为的「屏蔽」根本不够

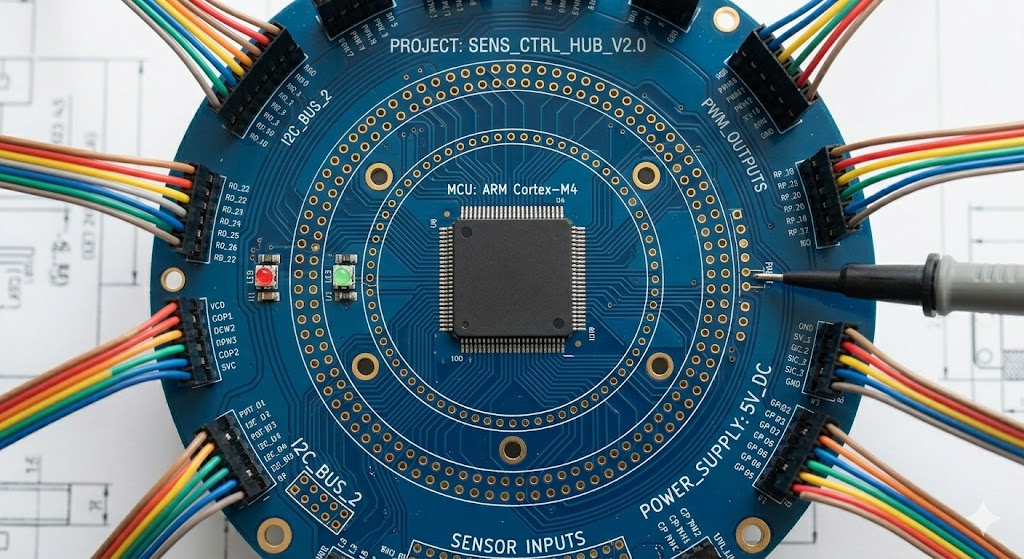

典型设计缺陷: - 四层板设计中缺失完整的GND平面 - 射频走线未做50Ω阻抗控制 - 屏蔽罩开孔直径超过λ/20

实测案例: 某门锁使用ESP32-WROOM模组时,在748MHz频点超标8dB。根本原因是: 1. 天线馈线长度达到λ/4(约10cm) 2. PCB第2层存在3mm宽的电源分割槽 3. 屏蔽罩接地点数量不足(每边<3个)

完整验证步骤: 1. 预扫描阶段(研发端): - 使用近场探头定位辐射热点 - 检查所有跨分割区域的信号线 2. 正式测试阶段(认证端): - 在3m电波暗室进行30MHz~1GHz全频段扫描 - 重点监控Wi-Fi(2.4GHz)与868MHz子频段的谐波交叉点 3. 整改措施: - 采用0.8mm厚镀锌钢板屏蔽罩(需开模) - 在电源入口增加π型滤波电路(10μH+0.1μF+10μH) - 修改PCB叠层为完整地平面设计

2. 欧洲868MHz频段是死亡陷阱

协议层致命问题: ESP32默认固件存在三项不符合EN 300 220-1标准的行为: 1. 缺省发射功率超过17dBm上限 2. 未实现Listen Before Talk(LBT)算法 3. 占空比超限(实际达10%,标准要求≤1%)

硬件改造方案对比:

| 方案 | 成本 | 性能影响 | 产线良率 |

|---|---|---|---|

| 外置SAW滤波器 | ¥2.3/台 | 插损增加1.2dB | 98% |

| 更换SiP模块 | ¥15.6/台 | 无额外损耗 | 99.5% |

| 重构PCB天线匹配网络 | ¥0.5/台 | 需重新调谐 | 95% |

软件适配关键点: 1. 修改esp-idf的phy_init_data.h参数:

#define RF_TX_POWER_DBM 17 // 原值为20

#define LBT_RSSI_THRESHOLD -65 // 单位dBm3. 你的OTA更新正在裸奔

安全架构常见漏洞: 1. 传输层:使用HTTP明文传输固件 2. 存储层:密钥存放在可读的Flash分区 3. 验证层:仅做CRC校验而无数字签名

合规改造路径:

硬件层面: - 必须采用安全元件(Secure Element): - 推荐型号:ATECC608A-MAHCZ-T - 关键参数: - 真随机数生成器(TRNG) - 支持ECDSA P-256签名 - 防拆解金属防护层

软件层面: 1. 实现端到端加密流程:

固件包 -> AES-256加密 -> ECDSA签名 -> 安全传输 -> 验签 -> 解密可复用的工程化checklist

研发阶段验证项

- 射频预兼容测试:

- [ ] 使用频谱仪扫描30MHz-6GHz全频段

- [ ] 检查所有时钟信号的谐波成分

-

[ ] 验证屏蔽罩接地点阻抗<50mΩ

-

协议合规测试:

- [ ] 记录LBT响应时间直方图

- [ ] 验证占空比统计分布

-

[ ] 执行200次连续跳频测试

-

安全测试:

- [ ] 尝试通过JTAG接口读取Flash

- [ ] 监测电源纹波分析密钥特征

- [ ] 执行10万次暴力破解尝试

生产阶段管控项

| 检查项目 | 标准方法 | 抽样比例 | 接受标准 |

|---|---|---|---|

| 屏蔽罩焊接质量 | X光检测 | 5% | 无虚焊/气泡 |

| SAW滤波器中心频率 | 网络分析仪 | 3% | 868.3MHz±0.2MHz |

| 安全芯片密钥注入 | HSM签名验证 | 100% | 签名验证通过 |

反常识的性价比方案

CE认证的EMC实验室单次测试报价高达¥8万,但通过以下低成本方案可提前拦截90%问题:

- 研发端替代方案:

- 使用Rigol DSA815+近场探头(总成本<¥3万)

-

建立简易GTEM小室(成本约¥5000)

-

开源工具链:

# 使用esptool.py验证Flash安全配置 esptool.py --port /dev/ttyUSB0 read_flash_status # 期待返回值:0x1C(安全启动+Flash加密使能) -

关键指标提前验证:

- 在-40℃~85℃温度循环下测试射频稳定性

- 用静电枪执行±8kV接触放电测试

合规设计不是产品开发的最后一道工序,而是贯穿从芯片选型到生产测试的全流程生命线。那些认为"先做出功能再整改"的团队,最终都在血淋淋的认证失败和市场召回中付出了更高代价。

更多推荐

已为社区贡献1000条内容

已为社区贡献1000条内容

所有评论(0)