MEGA88单片机232串口通信程序深度解析与实战

AVR MEGA88采用哈佛架构,具备独立的程序与数据总线,运行效率高。其CPU由算术逻辑单元(ALU)、寄存器文件(32个通用寄存器)和控制单元组成,支持单周期指令执行,显著提升处理速度。系统时钟由外部或内部振荡器提供,经分频器驱动CPU及外设模块。传统TTL/CMOS逻辑电路使用0V表示逻辑“0”,+5V或+3.3V表示逻辑“1”。然而,RS-232采用了完全不同的电压体系——它通过负电压代表

简介:MEGA88单片机在工业控制、数据采集和通信系统中广泛应用,其内置的UART接口支持高效的串行通信。本文围绕MEGA88 232程序,深入讲解基于RS-232标准的串口通讯实现方法,涵盖波特率设置、寄存器配置、数据发送与接收机制,并扩展至双串口通信的应用场景。结合源码注释文件(www.pudn.com.txt),帮助开发者掌握单片机串口编程的核心技术,提升嵌入式系统开发能力。

1. MEGA88单片机架构与UART资源概述

MEGA88核心架构概览

AVR MEGA88采用哈佛架构,具备独立的程序与数据总线,运行效率高。其CPU由算术逻辑单元(ALU)、寄存器文件(32个通用寄存器)和控制单元组成,支持单周期指令执行,显著提升处理速度。系统时钟由外部或内部振荡器提供,经分频器驱动CPU及外设模块。

片上外设与I/O端口映射

MEGA88集成多个可编程外设,包括两个USART模块(USART0和USART1),支持全双工异步/同步串行通信。I/O端口(PORTB、PORTC、PORTD)通过方向寄存器(DDRx)配置输入输出,并与UART引脚(TXD0/RXD0, TXD1/RXD1)复用,需正确设置以启用通信功能。

USART模块在通信系统中的角色

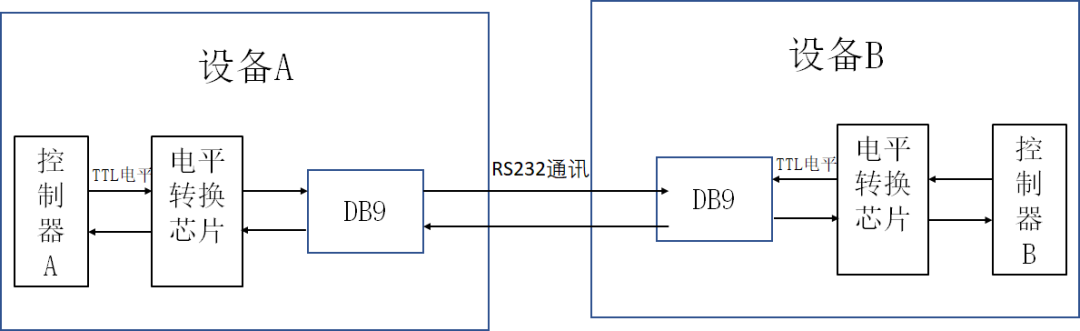

USART0和USART1均支持RS-232标准通信,通过电平转换芯片(如MAX232)实现TTL/CMOS与EIA电平互转。模块内置波特率发生器、数据帧控制器和状态标志寄存器,配合中断机制可高效完成串行数据收发,为嵌入式系统远程通信提供硬件基础。

2. RS-232通信标准详解与电气特性解析

RS-232是最早被广泛采用的串行通信标准之一,至今仍在工业控制、嵌入式调试和设备互联中发挥着不可替代的作用。尽管其传输速率相对较低、物理连接复杂,但因其协议简单、兼容性强,依然是许多微控制器(如AVR MEGA88)默认支持的基础通信接口。本章将从协议规范、物理层设计到时序匹配三个维度深入剖析RS-232的核心机制,尤其聚焦于其在实际硬件系统中的电气特性和实现方式。

2.1 RS-232协议的基本规范

作为国际电信联盟(ITU)制定的标准,RS-232定义了数据终端设备(DTE)与数据通信设备(DCE)之间的串行二进制数据交换格式。该标准不仅规定了逻辑电平、帧结构,还明确了信号线功能与时序要求,构成了一套完整的点对点异步通信体系。

2.1.1 信号电平定义与逻辑表示

传统TTL/CMOS逻辑电路使用0V表示逻辑“0”,+5V或+3.3V表示逻辑“1”。然而,RS-232采用了完全不同的电压体系——它通过负电压代表逻辑“1”,正电压代表逻辑“0”,这一反向逻辑设计源于早期电话线路抗干扰的需求。

根据EIA/TIA-232-F标准:

- 逻辑1(Mark) :电压范围为 -3V 至 -15V

- 逻辑0(Space) :电压范围为 +3V 至 +15V

- 无效区间(-3V ~ +3V) 被视为过渡态或噪声区域,接收器应忽略此范围内的信号

这种高幅值双极性电压设计具备较强的抗电磁干扰能力,适合长距离电缆传输。但在现代数字系统中,MCU通常运行于单电源(如+5V),无法直接产生±12V电压,因此必须借助专用电平转换芯片完成桥接。

MAX232电平转换芯片工作原理

MAX232是一款典型的RS-232收发器IC,内部集成电荷泵电路,可由单一+5V电源生成±10V左右的双电源电压,用于驱动RS-232输出级。其主要引脚包括:

| 引脚 | 名称 | 功能说明 |

|---|---|---|

| T1IN | 发送输入 | 接MCU的TXD引脚(TTL电平) |

| T1OUT | 发送输出 | 输出RS-232电平至外部设备 |

| R1IN | 接收输入 | 接外部RS-232信号 |

| R1OUT | 接收输出 | 输出TTL电平至MCU的RXD引脚 |

| C1+, C1-, C2+, C2- | 外部电容连接端 | 用于构建电压倍增电路 |

// 示例:MAX232典型外围电路连接(非代码执行)

/*

VCC (+5V)

|

=== C1 (1uF)

| |

C1+ C1-

| |

MAX232

| |

C2+ C2-

| |

=== C2 (1uF)

|

GND

*/

逻辑分析 :MAX232内部电荷泵利用振荡器和开关电容网络,在C1和C2两个外部小电容的配合下,将+5V升压为约+10V,并反相生成-10V。这些电压供给片内驱动器使用,使得T1OUT能够在空闲状态维持负压(逻辑1),而在发送时切换为正压(逻辑0)。R1IN则通过比较器检测输入电压极性,还原成TTL电平输出至R1OUT。

该芯片通常包含两组收发通道(T1/R1 和 T2/R2),允许同时处理多个串口信号。由于其无需额外电源即可完成电平转换,成为MEGA88等单片机实现RS-232通信的关键桥梁。

2.1.2 数据帧格式构成

RS-232采用异步串行通信方式,即没有共享时钟线,发送方与接收方依靠预设的波特率同步采样时间。每个字符以“数据帧”为单位独立封装传输,基本结构如下图所示(使用mermaid流程图描述):

sequenceDiagram

participant Sender

participant Wire

participant Receiver

Sender->>Wire: 空闲状态(高电平,逻辑1)

Wire->>Receiver: 持续高电平

Sender->>Wire: 起始位(低电平,逻辑0)

Wire->>Receiver: 检测下降沿,启动定时

loop 每位持续时间 = 1/Baud

Sender->>Wire: 数据位 D0-D7(LSB先发)

end

opt 奇偶校验位

Sender->>Wire: 校验位(0或1)

end

Sender->>Wire: 停止位(1~2个高电平)

Wire->>Receiver: 恢复空闲状态

一个完整的数据帧由以下部分组成:

- 起始位(Start Bit) :固定为逻辑0,标志一帧开始。

- 数据位(Data Bits) :长度可选5~9位,常用为8位(一个字节)。低位(LSB)先行。

- 奇偶校验位(Parity Bit) (可选):用于简单错误检测,分为:

- 无校验(None)

- 偶校验(Even):使整个帧中“1”的总数为偶数

- 奇校验(Odd):使“1”的总数为奇数 - 停止位(Stop Bit) :逻辑1,表示帧结束,长度可为1、1.5或2位。

常见配置命名规则为: 数据位-校验类型-停止位 ,例如:

| 配置 | 含义 | 总位数(8数据位) |

|---|---|---|

| 8-N-1 | 8位数据,无校验,1位停止 | 10位 |

| 7-E-1 | 7位数据,偶校验,1位停止 | 9位 |

| 8-O-2 | 8位数据,奇校验,2位停止 | 12位 |

假设使用9600 bps的波特率发送“Hello”字符串(ASCII码:’H’=0x48),采用8-N-1配置,则每秒可传输:

\frac{9600}{10} = 960 \text{ 字符/秒}

这意味着每个字符耗时约1.04ms。若需提升吞吐量,可选择更高波特率(如115200),但需确保通信双方严格同步且线路质量良好。

2.2 物理层连接与引脚定义

虽然RS-232协议本身不强制规定连接器类型,但在PC与外设之间最常用的接口是DB9(9针D型连接器)。了解其引脚定义对于正确布线至关重要。

2.2.1 典型信号线功能说明

以下是RS-232通信中最关键的五条信号线及其作用:

| 信号线 | 方向 | 功能描述 |

|---|---|---|

| TXD(Transmit Data) | DTE → DCE | 发送数据 |

| RXD(Receive Data) | DTE ← DCE | 接收数据 |

| RTS(Request To Send) | DTE → DCE | 表示DTE准备发送 |

| CTS(Clear To Send) | DTE ← DCE | DCE允许DTE发送 |

| GND(Signal Ground) | 双向 | 所有信号共用地线 |

其中, GND是必须连接的参考地 ,否则电平无法正确识别;而RTS/CTS属于硬件流控信号,用于防止缓冲区溢出,在低速或短距离通信中常被省略。

2.2.2 DB9接口引脚对应关系及直连/交叉接法选择

DB9母头(常见于PC)引脚定义如下:

| 引脚号 | 信号名 | 缩写 |

|---|---|---|

| 1 | Data Carrier Detect | DCD |

| 2 | Received Data | RXD |

| 3 | Transmitted Data | TXD |

| 4 | Data Terminal Ready | DTR |

| 5 | Signal Ground | GND |

| 6 | Data Set Ready | DSR |

| 7 | Request To Send | RTS |

| 8 | Clear To Send | CTS |

| 9 | Ring Indicator | RI |

当连接两台设备时,必须注意“同类设备对接”还是“异类设备对接”:

- DTE ↔ DCE(如PC ↔ 调制解调器) :使用 直连线 (Pin-to-Pin)

- DTE ↔ DTE(如PC ↔ 单片机系统) :使用 交叉线(Null Modem Cable)

典型交叉连接方式如下表:

| 设备A(DTE) | 连接到 | 设备B(DTE) |

|---|---|---|

| Pin 2 (RXD) | → | Pin 3 (TXD) |

| Pin 3 (TXD) | → | Pin 2 (RXD) |

| Pin 5 (GND) | → | Pin 5 (GND) |

| (可选)Pin 7 (RTS) | → | Pin 8 (CTS) |

| (可选)Pin 4 (DTR) | → | Pin 6 (DSR) |

graph LR

A[PC]

B[MEGA88开发板]

A -- "TXD(3)" -->|交叉| B_RXD

B_TXD -- "RXD(2)" -->|交叉| A

A -- "GND(5)" --> B_GND

style A fill:#f9f,stroke:#333

style B fill:#bbf,stroke:#333

图解:PC与MEGA88均为DTE设备,需交叉TXD/RXD并共地才能通信。

2.2.3 通信距离限制与噪声抑制策略

RS-232标准规定的最大电缆长度为 50英尺(约15米) ,但这取决于波特率和电缆质量。高频信号在长线上易受电容效应衰减,导致边沿畸变,进而引发采样错误。

影响有效通信距离的因素包括:

| 因素 | 影响机制 | 改善方法 |

|---|---|---|

| 波特率过高 | 单位时间内信号变化快,易失真 | 降低波特率 |

| 电缆分布电容大 | 导致上升/下降沿变缓 | 使用屏蔽双绞线 |

| 地电位差 | GND偏移造成误判 | 加装光电隔离或使用RS-485替代 |

| 电磁干扰(EMI) | 引入虚假跳变 | 增加磁环、远离动力线 |

推荐的噪声抑制措施包括:

- 使用带屏蔽层的双绞线 :减少串扰和感应噪声;

- 缩短走线长度 :尽量控制在10米以内;

- 添加瞬态电压抑制二极管(TVS) :保护接口免受静电放电(ESD)损坏;

- 光耦隔离 :在工业环境中切断地环路,提高共模抑制比。

例如,在恶劣工厂环境下,即使使用MAX232也无法稳定通信时,可考虑升级为RS-485总线方案,支持多点、远距离、差分传输。

2.3 波特率标准与时序匹配要求

波特率(Baud Rate)是指每秒传输的符号数,在RS-232中通常等于每秒传输的位数(bit/s)。它是决定通信速度和可靠性的核心参数。

2.3.1 常用波特率值及其应用场景

标准化的波特率源自早期电话调制解调器的技术演进,当前主流值包括:

| 波特率 | 应用场景 | 特点 |

|---|---|---|

| 9600 | 调试信息输出、传感器通信 | 兼容性好,稳定性高 |

| 19200 | 中速设备通信 | 平衡速度与误差容忍度 |

| 38400 | 工业PLC、HMI交互 | 较高速率仍保持较好精度 |

| 115200 | 快速日志上传、固件更新 | 接近极限,需精确时钟源 |

例如,在MEGA88上使用1MHz内部RC振荡器配置115200波特率时,计算得UBRR ≈ 0,实际误差超过10%,极易导致接收失败。因此高波特率应用必须搭配精准外部晶振(如8MHz或16MHz)。

2.3.2 发送与接收双方的波特率一致性约束

由于RS-232为异步通信,接收端依赖本地时钟重建比特流。若双方波特率偏差过大,采样点会逐渐漂移,最终在停止位前发生误判。

假设发送方以理想周期 $ T_s = 1/Baud $ 发送,接收方使用周期 $ T_r $ 采样,则每帧累计误差为:

\Delta t_{\text{per bit}} = |T_s - T_r|

经过N个数据位后,总偏差达 $ N \cdot \Delta t $,必须小于半个位宽才可正确识别:

N \cdot |\Delta t| < \frac{T}{2}

\Rightarrow \left|\frac{f_r - f_s}{f_s}\right| < \frac{1}{2N}

以8-N-1帧为例(共10位),允许的最大频率误差为:

\frac{1}{2 \times 10} = 5\%

但考虑到起始位检测存在±0.5位不确定性,实际工程中普遍接受的 最大容错率为±2% 。

2.3.3 容忍误差范围分析

不同波特率下允许的时钟偏差阈值不同。下表列出常见组合的误差容忍情况:

| 波特率 | 最大允许误差(±%) | 对应时钟精度需求(ppm) |

|---|---|---|

| 9600 | 2% | ±20,000 ppm |

| 19200 | 2% | ±20,000 ppm |

| 115200 | 1.5% | ±15,000 ppm |

注:1% = 10,000 ppm(parts per million)

以ATmega88使用内部RC振荡器为例,出厂校准精度约为±10%,温度变化下可达±30%,显然不适合高于9600的波特率。而使用16MHz ±20ppm晶振时,误差仅0.002%,完全满足所有标准波特率需求。

此外,AVR USART模块提供 双速模式(U2X) ,可通过设置UCSRA寄存器中的U2X位,使波特率发生器分频系数从16降为8,从而在相同UBRR值下实现两倍速率,同时提升低频下的精度表现。

// 设置双速模式以改善波特率精度

UCSRA |= (1 << U2X);

// 计算UBRR时需调整公式:

// UBRR = (F_CPU / (8 * BAUD)) - 1 (当U2X=1时)

参数说明 :

-U2X: 双速模式使能位,设为1时波特率发生器使用8倍频而非16倍频

- 优点:提高UBRR寄存器分辨率,减小舍入误差

- 缺点:最高波特率受限(因采样率翻倍)

综上所述,RS-232虽看似简单,实则涉及精密的电气匹配与时序协调。只有充分理解其底层机制,才能在MEGA88等资源有限的平台上构建稳定可靠的串行通信链路。

3. MEGA88 USART寄存器体系与初始化配置

在嵌入式系统开发中,串行通信是实现设备间数据交换的基础手段之一。AVR MEGA88微控制器集成了两个高性能的USART(通用同步/异步收发器)模块——USART0 和 USART1,支持全双工异步通信、同步主从模式以及多处理器通信模式。要充分发挥其功能,必须深入理解其底层寄存器体系结构,并掌握正确的初始化流程。本章将系统性地解析 MEGA88 的 USART 核心寄存器群组,详细说明每个控制与状态位的功能语义,并通过代码示例展示如何基于这些寄存器构建稳定可靠的串口通信基础。

3.1 USART核心寄存器概览

MEGA88 的 USART 模块由一组专用寄存器构成,它们分布在不同的 I/O 地址空间中,用于配置工作模式、设置波特率、传输数据以及监控通信状态。这组寄存器主要包括: UDR (数据寄存器)、 UBRRH/UBRRL (波特率寄存器高/低字节)、 UCSRA (控制和状态寄存器 A)、 UCSRB (控制和状态寄存器 B)以及 UCSRC (控制和状态寄存器 C)。这些寄存器共同决定了 USART 的运行行为。

3.1.1 UDR:数据寄存器——发送与接收共用的数据通道

UDR (USART Data Register)是用户与 USART 模块交互的核心接口。尽管它只有一个名称和地址,但实际上内部存在两个独立的 8 位寄存器:一个用于接收(RxD),另一个用于发送(TxD)。当执行写操作时,CPU 将待发送的数据写入 TxD 寄存器;当执行读操作时,则从 RxD 寄存器中取出接收到的数据。

这种“一址双用”的设计依赖于 CPU 访问方向自动区分用途:

- 写 UDR → 启动发送过程

- 读 UDR → 获取已接收的数据

// 示例:直接访问 UDR 发送单字节

UDR = 'A'; // 将字符 'A' 写入发送缓冲区

需要注意的是,在发送前必须确保 UDRE (数据寄存器空)标志位已被置位,否则新写入的数据可能覆盖尚未移位完成的旧数据,导致通信错误。同样,在读取 UDR 前应确认 RXC (接收完成)标志有效,以避免读取无效或过期数据。

数据通路逻辑分析

下图展示了 MEGA88 USART 中 UDR 在发送与接收路径中的角色:

graph TD

A[CPU Write to UDR] --> B[TxD Buffer]

B --> C[Shift Register (Transmit)]

C --> D[TXD Pin Output]

E[RXD Pin Input] --> F[Shift Register (Receive)]

F --> G[RxD Buffer]

G --> H[CPU Read from UDR]

style A fill:#e6f7ff,stroke:#333

style H fill:#e6f7ff,stroke:#333

该流程图清晰地表明,无论是发送还是接收, UDR 都作为最终的数据入口和出口,而中间的移位寄存器负责按位串行化处理。这一机制保证了并行到串行转换的透明性,使开发者可以专注于高层协议而非物理层细节。

3.1.2 UBRRH与UBRRL:波特率寄存器高/低字节设置

波特率生成依赖于一个 12 位的预分频计数器,该计数器由两个 8 位寄存器组成: UBRRH (高字节)和 UBRRL (低字节)。其中, UBRRH 的低 4 位( URSEL 除外)与 UBRRL 构成完整的 12 位值,表示波特率分频系数 UBRR 。

计算公式如下:

\text{UBRR} = \frac{F_{\text{CPU}}}{16 \times \text{BAUD}} - 1 \quad (\text{标准模式})

若启用双速模式(U2X=1),则使用除以 8 的公式:

\text{UBRR} = \frac{F_{\text{CPU}}}{8 \times \text{BAUD}} - 1

假设系统使用 16 MHz 晶振,目标波特率为 9600 bps,采用标准模式:

\text{UBRR} = \frac{16,000,000}{16 \times 9600} - 1 = 103.166 \approx 103

因此需将 UBRRH = 0x06 , UBRRL = 0x07 (因为 103 = 0x67)。

以下是设置 UBRR 的典型 C 语言代码段:

#define F_CPU 16000000UL

#define BAUD 9600

#include <util/setbaud.h>

// 使用 <util/setbaud.h> 自动生成 UBRR 值

void uart_init(void) {

UBRRH = (uint8_t)(UBRR_VALUE >> 8);

UBRRL = (uint8_t)UBRR_VALUE;

#ifdef U2X

UCSRA |= (1 << U2X);

#else

UCSRA &= ~(1 << U2X);

#endif

// ... 其他初始化

}

参数说明与逻辑分析

UBRR_VALUE和U2X是<util/setbaud.h>根据F_CPU和BAUD宏自动计算出的推荐值;- 移位操作

(UBRR_VALUE >> 8)提取高 8 位写入UBRRH; - 强制类型转换为

uint8_t确保只写入低字节部分; - 条件编译确保根据是否需要更高精度选择 U2X 模式。

此方法优于手动计算,能自动处理四舍五入误差并提示潜在的波特率偏差。

3.1.3 UCSRA、UCSRB、UCSRC:控制与状态寄存器功能划分

这三个寄存器构成了 USART 的核心控制中枢,分别承担状态反馈、功能使能和模式设定任务。

| 寄存器 | 主要职责 |

|---|---|

| UCSRA | 包含运行状态标志(如 TXC, UDRE)及双速模式控制 |

| UCSRB | 控制发送/接收使能、中断允许等关键功能 |

| UCSRC | 设定帧格式(数据位、停止位、校验方式)、同步/异步模式 |

值得注意的是, UCSRC 和 UBRRH 共享同一个 I/O 地址(0x40),其选择由 URSEL 位决定:

- 当写入时 URSEL = 1 → 配置 UCSRC

- 当写入时 URSEL = 0 → 配置 UBRRH

这是一个容易出错的设计点,务必注意顺序和位设置。

下面列出各寄存器的关键位定义表:

| UCSRA Bit | 名称 | 功能描述 |

|---|---|---|

| 7: RXC | 接收完成标志 | 数据从移位寄存器移入 RxB 时置位,读 UDR 后清零 |

| 6: TXC | 发送完成标志 | 最后一位(停止位)发送完毕后置位,可软件清零 |

| 5: UDRE | 数据寄存器空 | 表示 TxD 缓冲区为空,可写入新数据 |

| 1: U2X | 双倍传输速率 | 提升波特率精度,降低误差 |

| UCSRB Bit | 名称 | 功能描述 |

|---|---|---|

| 4: RXEN | 接收使能 | 置 1 开启接收功能 |

| 3: TXEN | 发送使能 | 置 1 开启发送功能 |

| 7: RXCIE | 接收中断允许 | 置 1 允许接收完成触发中断 |

| UCSRC Bit | 名称 | 功能描述 |

|---|---|---|

| 7: URSEL | 寄存器选择 | 必须为 1 才能写入 UCSRC |

| 6: UMSEL | 模式选择 | 0=异步, 1=同步 |

| 5~4: UPM | 奇偶校验模式 | 00=无校验, 11=保留, 10=偶校验, 01=奇校验 |

| 3: USBS | 停止位数 | 0=1位, 1=2位 |

| 2~1: UCSZ | 字长选择 | 配合 UCSZ2 在 UCSRB 中决定数据位长度 |

这些位的组合直接影响通信帧的构造,任何配置错误都将导致对方无法正确解析数据。

3.2 控制寄存器详细配置方法

正确配置控制寄存器是实现可靠串口通信的前提。每一比特都具有特定含义,且多个寄存器之间存在协同关系。以下逐项解析三大控制寄存器中的关键字段及其配置策略。

3.2.1 UCSRA 寄存器标志位解析

UCSRA 是状态感知的核心来源,包含三个最重要的标志位: RXC 、 TXC 和 UDRE 。

RXC(接收完成)

当 USART 完成一帧数据的接收并将内容载入 UDR 后, RXC 被硬件置位。若同时启用了接收中断( RXCIE=1 ),则触发 ISR。该标志可通过读取 UDR 自动清除。

应用场景示例:

while (!(UCSRA & (1 << RXC))); // 查询等待接收完成

char c = UDR; // 读取数据,自动清 RXC

TXC(发送完成)

TXC 表示整个数据帧(包括停止位)已从移位寄存器输出至 TXD 引脚。常用于确认最后一帧发送结束,适用于需要精确同步的场合(如总线释放、电源切换)。

手动清零方式:

UCSRA |= (1 << TXC); // 写 1 清零(特殊操作)

UDRE(数据寄存器空)

UDRE 是发送流程的关键判据。只要发送缓冲区为空(即上一字节已进入移位寄存器),此位即被置起,表示可安全写入下一字节。

典型轮询发送函数片段:

void uart_putc(char c) {

while (!(UCSRA & (1 << UDRE))); // 等待缓冲区空

UDR = c;

}

该机制避免了数据覆盖问题,是实现阻塞式发送的基础。

3.2.2 UCSRB 寄存器使能控制

UCSRB 控制着 USART 的基本功能开关,尤其是发送与接收的使能状态以及中断响应能力。

RXEN 与 TXEN:收发使能

这两个位分别开启接收和发送电路。一旦置位,相应的引脚(RXD/TXD)将脱离普通 GPIO 模式,转为专用串行通信引脚。

重要约束:

- 若未设置 RXEN ,即使有数据到达也不会触发中断或填充 UDR;

- 若未设置 TXEN ,则无法启动发送, UDRE 永远不会置位。

初始化时通常两者均开启:

UCSRB = (1 << RXEN) | (1 << TXEN); // 开启收发功能

RXCIE:接收中断允许

若希望采用中断驱动方式处理接收数据,必须设置 RXCIE = 1 ,并配合全局中断使能 sei() 。

中断服务例程模板:

ISR(USART_RXC_vect) {

char received_char = UDR;

ring_buffer_put(&rx_buf, received_char);

}

中断方式显著降低 CPU 轮询开销,特别适合实时系统或多任务环境。

3.2.3 UCSRC 寄存器模式设定

UCSRC 决定了通信的基本帧结构,是配置中最易出错的部分之一。

URSEL:寄存器选择位

由于 UCSRC 与 UBRRH 共享地址,写入时必须明确指定 URSEL = 1 才能修改 UCSRC 。常见错误是在没有设置 URSEL 的情况下尝试配置模式参数。

正确写法:

UCSRC = (1 << URSEL) | (1 << UCSZ1) | (1 << UCSZ0); // 设置 8 数据位

错误写法(可能导致 UBRRH 被误改):

UCSRC = (1 << UCSZ1) | (1 << UCSZ0); // 缺少 URSEL,实际修改的是 UBRRH!

UPM:奇偶校验模式

奇偶校验提供简单的错误检测机制。常用配置如下:

| UPM1 | UPM0 | 模式 |

|---|---|---|

| 0 | 0 | 无校验 |

| 1 | 0 | 偶校验 |

| 1 | 1 | 奇校验 |

例如启用偶校验:

UCSRC |= (1 << UPM1); // UPM[1:0] = 10 → 偶校验

发送方和接收方必须一致,否则会持续报“奇偶错误”。

UCSZ:数据位长度选择

数据位长度由 UCSRC 中的 UCSZ1 和 UCSZ0 ,以及 UCSRB 中的 UCSZ2 共同决定:

| UCSZ2 | UCSZ1 | UCSZ0 | 数据位数 |

|---|---|---|---|

| 0 | 0 | 0 | 5 |

| 0 | 0 | 1 | 6 |

| 0 | 1 | 0 | 7 |

| 0 | 1 | 1 | 8 |

| 1 | 0 | 0 | 9 |

最常见的是 8 位数据( UCSZ1=1, UCSZ0=1 )。

完整设置示例:

UCSRC = (1 << URSEL) | (1 << UCSZ1) | (1 << UCSZ0); // 8N1

UCSRB &= ~(1 << UCSZ2); // 确保不是 9 位模式

3.3 初始化流程设计与代码实现框架

合理的初始化顺序对于确保 USART 正常工作至关重要。错误的配置顺序可能导致不可预测的行为,例如波特率错误、帧格式异常或中断失效。

3.3.1 设置波特率预分频参数

首先应配置 UBRRH 和 UBRRL ,确保在使能发送/接收前就具备正确的时钟基准。

void uart_init_baud_only(uint32_t baud) {

uint16_t ubrr = (F_CPU / (16UL * baud)) - 1;

UBRRH = (uint8_t)(ubrr >> 8);

UBRRL = (uint8_t)ubrr;

}

建议优先使用 <util/setbaud.h> 进行自动化计算,避免浮点误差。

3.3.2 配置数据格式(帧结构)

帧结构应在使能收发前完成设定。典型的 8-N-1 配置如下:

UCSRC = (1 << URSEL) | (1 << UCSZ1) | (1 << UCSZ0); // 8 data bits, no parity, 1 stop bit

UCSRB &= ~(1 << UCSZ2); // Not 9-bit mode

若需 2 停止位,添加 (1 << USBS) 。

3.3.3 使能发送与接收功能

最后一步才是开启 RXEN 和 TXEN ,防止在配置未完成时意外启动通信。

UCSRB |= (1 << RXEN) | (1 << TXEN);

3.3.4 启动中断机制(可选)

若使用中断接收,还需启用 RXCIE 并打开全局中断:

UCSRB |= (1 << RXCIE);

sei(); // __enable_interrupt()

完整初始化函数示例

#include <avr/io.h>

#include <avr/interrupt.h>

#include <util/setbaud.h>

void uart_init(void) {

// Step 1: Set baud rate

UBRRH = (uint8_t)(UBRR_VALUE >> 8);

UBRRL = (uint8_t)UBRR_VALUE;

// Step 2: Enable double speed if needed

#if defined(U2X)

UCSRA |= (1 << U2X);

#else

UCSRA &= ~(1 << U2X);

#endif

// Step 3: Set frame format: 8N1

UCSRC = (1 << URSEL) | (1 << UCSZ1) | (1 << UCSZ0);

// Step 4: Enable receiver and transmitter

UCSRB = (1 << RXEN) | (1 << TXEN);

// Step 5: Optional - enable RX interrupt

// UCSRB |= (1 << RXCIE);

}

int main(void) {

uart_init();

sei();

while (1) {

uart_putc('H');

_delay_ms(1000);

}

}

逻辑逐行解读

UBRRH/L设置由<util/setbaud.h>提供的精确值;- 条件编译处理 U2X 模式,优化波特率精度;

UCSRC明确设置URSEL=1,避免误写UBRRH;UCSRB同时启用收发,但暂不开启中断;- 主循环中周期发送字符 ‘H’,可用于串口助手验证。

该代码结构清晰、层次分明,符合工业级嵌入式编程规范,适用于大多数基于 MEGA88 的串口应用项目。

4. 波特率计算模型与串口初始化实战

在嵌入式系统开发中,串行通信的稳定性高度依赖于精确的波特率配置。AVR MEGA88单片机通过其内置的USART模块支持异步串行通信,但要实现可靠的数据收发,必须确保发送端与接收端使用一致且准确的波特率。本章将深入剖析波特率生成的数学原理,结合MEGA88的硬件架构特点,构建完整的初始化流程,并通过实际代码实现、波形验证和常见问题规避策略,全面掌握从理论到实践的完整闭环。

4.1 波特率生成数学模型

4.1.1 公式推导:UBRR = (F_CPU / (16 * BAUD)) - 1

MEGA88的USART模块在标准异步模式下采用一个基于系统时钟(F_CPU)的分频机制来生成目标波特率。该过程的核心是 波特率寄存器(UBRR) 的设置值计算,其基本公式如下:

\text{UBRR} = \frac{F_{CPU}}{16 \times \text{BAUD}} - 1

其中:

- $ F_{CPU} $:MCU主频,单位Hz;

- $ \text{BAUD} $:期望的波特率,如9600 bps;

- $ \text{UBRR} $:需写入UBRRL和UBRRH的12位整数值。

此公式的推导源于USART内部采样机制的设计。在标准模式下,接收器以16倍波特率对RXD引脚进行采样,即每比特时间划分为16个时钟周期,通过中间多个采样点判断电平状态,提高抗噪声能力。因此,每个比特持续时间为 $ \frac{1}{\text{BAUD}} $ 秒,对应的系统时钟周期数为:

T_{bit} = \frac{F_{CPU}}{\text{BAUD}} = 16 \times (\text{UBRR} + 1)

由此可得上述标准波特率计算公式。

精度要求分析

由于UBRR只能取整数,实际产生的波特率可能与理想值存在偏差。若误差过大(通常超过±2%),会导致接收端采样错位,引发帧错误或数据丢失。因此,在设计阶段必须评估该误差是否可接受。

例如,假设使用16MHz晶振,目标波特率为115200:

\text{UBRR} = \frac{16,000,000}{16 \times 115200} - 1 = \frac{16,000,000}{1,843,200} - 1 ≈ 8.68 - 1 = 7.68 → 取整为8

代入反算实际波特率:

\text{BAUD}_{actual} = \frac{16,000,000}{16 \times (8 + 1)} = \frac{16,000,000}{144} ≈ 111,111 \text{bps}

相对误差为:

\frac{|115200 - 111111|}{115200} ≈ 3.55\%

已超出推荐容限范围,说明在此条件下无法获得高精度通信,需考虑启用双速模式(U2X)或更换更高频率/更低分频比的配置方案。

4.1.2 不同晶振频率下的典型UBRR值对照表

为了便于快速选型和调试,下表列出了几种常用晶振频率与典型波特率组合下的UBRR计算结果及误差分析。

| F_CPU (MHz) | Baud Rate | UBRR 计算值 | 实际 UBRR | 实际 Baud | 误差 (%) |

|---|---|---|---|---|---|

| 1 | 9600 | (1M)/(16×9600)-1 ≈ 5.51 | 6 | 10417 | +8.5% |

| 8 | 9600 | (8M)/(16×9600)-1 ≈ 51.08 | 51 | 9804 | +2.1% |

| 8 | 38400 | (8M)/(16×38400)-1 ≈ 12.02 | 12 | 41667 | +8.5% |

| 16 | 9600 | (16M)/(16×9600)-1 ≈ 103.17 | 103 | 9615 | +0.16% |

| 16 | 19200 | (16M)/(16×19200)-1 ≈ 51.08 | 51 | 19608 | +2.1% |

| 16 | 115200 | (16M)/(16×115200)-1 ≈ 7.68 | 8 | 111111 | -3.55% |

结论 :在16MHz主频下,9600和19200波特率可实现较高精度;而115200则偏差较大,建议开启U2X模式改善。

4.1.3 双速模式(U2X)对精度的影响分析

AVR USART提供一种“双速模式”(由UCSRA寄存器中的U2X位控制),用于提升高速波特率下的精度表现。当U2X=1时,分频系数由16变为8,相应调整公式为:

\text{UBRR} = \frac{F_{CPU}}{8 \times \text{BAUD}} - 1

这使得在相同UBRR下波特率翻倍,或者在高速通信中减小量化误差。

示例对比(F_CPU = 16MHz, BAUD = 115200)

-

标准模式(U2X=0):

$$

\text{UBRR} = \frac{16,000,000}{16 × 115200} - 1 ≈ 7.68 → 8 \

\Rightarrow \text{Actual} = 111,111, \quad \text{Error} = -3.55\%

$$ -

双速模式(U2X=1):

$$

\text{UBRR} = \frac{16,000,000}{8 × 115200} - 1 ≈ 16.36 → 16 \

\Rightarrow \text{Actual} = \frac{16,000,000}{8 × 17} ≈ 117,647, \quad \text{Error} = +2.12\%

$$

虽然仍略有偏差,但优于标准模式。更重要的是,U2X允许更精细地逼近目标值,尤其适用于高波特率场景。

注意事项:

- 启用U2X会降低接收器采样点数量(从16降至8),略微削弱抗干扰能力。

- 某些低波特率下不应启用U2X,否则可能导致严重误差甚至通信失败。

- 建议仅在高波特率(≥38400)且标准模式误差超标时启用。

graph TD

A[开始] --> B{选择波特率和F_CPU}

B --> C[计算标准UBRR]

C --> D[检查误差是否<2%]

D -- 是 --> E[使用标准模式 U2X=0]

D -- 否 --> F[尝试U2X=1重新计算]

F --> G[再次评估误差]

G -- 仍超差 --> H[更换晶振或降低波特率]

G -- 可接受 --> I[配置U2X并写入UBRR]

I --> J[完成初始化]

4.2 实际初始化函数编写

4.2.1 C语言封装uart_init()函数结构

下面是一个针对MEGA88的通用串口初始化函数,支持多波特率配置与双速模式自动判断。

#include <avr/io.h>

#include <util/setbaud.h>

void uart_init(void) {

// 使用 <util/setbaud.h> 自动计算 UBRR 和 U2X 设置

#undef F_CPU

#define F_CPU 16000000UL

#define BAUD 9600

#include <util/setbaud.h>

UBRR0H = UBRRH_VALUE;

UBRR0L = UBRRL_VALUE;

#if USE_U2X == 1

UCSR0A |= (1 << U2X0); // 启用双速模式

#else

UCSR0A &= ~(1 << U2X0);

#endif

// 设置数据格式:8位数据,1位停止,无校验

UCSR0C = (1 << UCSZ01) | (1 << UCSZ00); // 8-bit data

UCSR0B = (1 << RXEN0) | (1 << TXEN0); // 使能收发

}

代码逻辑逐行解析:

#include <util/setbaud.h>:AVR libc 提供的头文件,可根据F_CPU和BAUD自动计算最优UBRR和U2X配置。#undef F_CPU/#define F_CPU ...:明确指定主频,避免宏定义冲突。#define BAUD ...:设定目标波特率。- 再次包含

<util/setbaud.h>触发内部计算,生成UBRRH_VALUE,UBRRL_VALUE,USE_U2X等符号。 UBRR0H/L = ...:将计算出的UBRR值写入高低字节寄存器。#if USE_U2X == 1:根据库建议决定是否启用U2X模式。UCSR0C设置数据位长度(UCSZ01:UCSZ00 = 0b11 表示8位)。UCSR0B使能接收(RXEN0)和发送(TXEN0)功能。

⚠️ 注意:

<util/setbaud.h>必须在定义了F_CPU和BAUD后包含,且不能用于运行时动态切换波特率。

4.2.2 条件编译支持多波特率切换

可通过预处理器宏实现多种波特率编译选项:

#define UART_BAUD_RATE 115200 // 可改为 9600, 19200 等

void uart_init_dynamic(void) {

#if UART_BAUD_RATE == 9600

#define BAUD 9600

#elif UART_BAUD_RATE == 19200

#define BAUD 19200

#elif UART_BAUD_RATE == 115200

#define BAUD 115200

#else

#error "Unsupported baud rate"

#endif

#define F_CPU 16000000UL

#include <util/setbaud.h>

UBRR0H = UBRRH_VALUE;

UBRR0L = UBRRL_VALUE;

#if USE_U2X == 1

UCSR0A |= (1 << U2X0);

#else

UCSR0A &= ~(1 << U2X0);

#endif

UCSR0C = (1 << UCSZ01) | (1 << UCSZ00);

UCSR0B = (1 << RXEN0) | (1 << TXEN0);

}

这种方式允许开发者通过修改宏定义快速切换波特率,适合不同项目复用。

4.2.3 错误检测与溢出标志处理

在初始化完成后,应定期检查状态寄存器以排除潜在异常:

void uart_check_errors(void) {

if (UCSR0A & (1 << FE0)) {

// 帧错误:停止位未正确检测

}

if (UCSR0A & (1 << DOR0)) {

// 数据溢出:新数据到达时前一字节未读取

}

if (UCSR0A & (1 << UPE0)) {

// 奇偶校验错误

}

// 清除错误标志(读UCSR0A后写UDR即可)

}

这些标志应在中断服务程序或主循环中监控,防止累积错误影响通信质量。

4.3 硬件验证手段

4.3.1 使用示波器观测TXD引脚波形

最直接的验证方式是使用示波器连接至TXD引脚(PD1),发送已知字符(如‘A’=0x41),观察其波形特征。

以9600波特率为例,每位宽度应为:

T_{bit} = \frac{1}{9600} ≈ 104.17 \mu s

ASCII字符 ‘A’(0b01000001)的帧结构(8-N-1)包括:

- 起始位:0(1 bit)

- 数据位:0x41 = 0b01000001(LSB先发)

- 无奇偶校验

- 停止位:1(1 bit)

总帧长10位,持续约1.04ms。

通过测量起始位到第一位数据的时间间隔,可以确认波特率准确性。若实测周期偏离理论值超过2%,需重新检查UBRR或U2X设置。

4.3.2 串口调试助手接收测试字符

使用PC端串口工具(如PuTTY、XCOM、SSCOM)连接至MAX232转换芯片输出端,设置相同波特率、数据格式,发送字符串:

void uart_putc(char c) {

while (!(UCSR0A & (1 << UDRE0))); // 等待缓冲区空

UDR0 = c;

}

void uart_puts(const char* str) {

while (*str) uart_putc(*str++);

}

// 测试调用

int main(void) {

uart_init();

while (1) {

uart_puts("Hello MEGA88!\r\n");

_delay_ms(1000);

}

}

若PC端能稳定接收到清晰文本,则表明初始化成功。

4.3.3 计算实际传输速率并与理论值对比

通过记录发送N个字符所耗时间(可用定时器或逻辑分析仪),计算有效吞吐量:

\text{Throughput} = \frac{N \times 10 \text{ bits}}{T_{total}} \quad \text{(bits/sec)}

例如发送100个字符耗时1.05秒:

\text{Rate} = \frac{100 × 10}{1.05} ≈ 952 bps → 接近9600预期值

若显著偏低,可能是由于软件阻塞、中断延迟或波特率配置错误所致。

4.4 常见配置陷阱与规避措施

4.4.1 晶振未启用内部锁相环导致波特率偏差

某些开发板默认使用内部RC振荡器(如8MHz),而非外部晶体。若未正确配置熔丝位(fuse bits)启用外部晶振,MCU仍以较低精度运行,造成波特率漂移。

解决方案 :

- 使用编程器(如USBasp)读取当前熔丝设置;

- 确保 CKSEL 位配置为外部晶振模式;

- 如使用16MHz晶振,应禁用内部PLL,保持 CLKPR 为默认值。

4.4.2 忘记设置全局中断使能(SEI指令)

当中断方式用于接收或发送时,即使设置了 RXCIE 或 UDRIE ,若未执行 sei() 启用全局中断,ISR不会触发。

#include <avr/interrupt.h>

void uart_enable_rx_interrupt(void) {

UCSR0B |= (1 << RXCIE0); // 使能接收中断

sei(); // 必须调用!否则中断不工作

}

这是初学者最常见的疏忽之一,表现为“中断函数写了但不执行”。

4.4.3 数据位或停止位不匹配引发乱码问题

若MCU设置为7-E-1(7数据位+偶校验+1停止位),而PC端设为8-N-1,则接收方解析错误,出现乱码或乱序。

排查方法 :

- 统一两端配置;

- 使用示波器查看帧结构;

- 发送固定模式字节(如0xFF)观察实际电平序列。

可通过以下表格辅助判断:

| 字符 | 预期波形(8-N-1) | 异常表现(7-E-1错配) |

|---|---|---|

| ‘A’(0x41) | LSB=1→0→0→0→0→0→1→0 | 解析为两个字符或乱码 |

| ‘Z’(0x5A) | 0→1→0→1→1→0→1→0 | 可能丢失高位或加错校验 |

综上所述,波特率配置不仅是简单的数学运算,更是涉及系统时钟、硬件连接、软件逻辑和外部设备协同的综合性工程任务。只有通过严谨建模、精准编码和充分验证,才能保障串口通信的长期稳定运行。

5. 串口数据发送机制实现与优化策略

在嵌入式系统开发中,串行通信是设备间信息交换的重要手段。MEGA88单片机通过其内置的USART模块提供了可靠的UART通信能力,其中 数据发送机制的设计质量直接影响系统的响应性、资源利用率和整体稳定性 。本章将深入探讨基于MEGA88平台的两种主要发送方式——查询(轮询)模式与中断驱动模式,并从底层寄存器操作到高级缓冲结构设计,全面解析其实现原理与性能优化路径。

5.1 查询方式发送(轮询UDRE标志)

查询方式是最基础的数据发送方法,适用于低负载或实时性要求不高的场景。该方法通过不断检测 UDRE (USART Data Register Empty)标志位来判断是否可以向数据寄存器写入下一个字节。

5.1.1 单字节发送函数uart_putc()设计

void uart_putc(uint8_t data) {

// 等待UDRE标志置位,表示发送缓冲区为空

while (!(UCSRA & (1 << UDRE))) {

// 轮询等待,期间CPU无法执行其他任务

}

// 将数据写入UDR寄存器,启动发送过程

UDR = data;

}

代码逻辑逐行分析:

| 行号 | 代码片段 | 参数说明与功能解释 |

|---|---|---|

| 1 | void uart_putc(uint8_t data) |

函数接收一个8位无符号整数作为待发送字符,类型为 uint8_t ,符合ASCII编码范围。 |

| 3 | while (!(UCSRA & (1 << UDRE))) |

检查UCSRA寄存器中的UDRE位是否为1。若未置位,说明发送器仍在处理前一字节,需持续等待。 (1 << UDRE) 生成对应位掩码。 |

| 4 | { } |

空循环体构成阻塞式等待,直到硬件自动设置UDRE标志。此期间MCU不能进行有效工作,造成CPU浪费。 |

| 6 | UDR = data; |

一旦UDRE置位,立即向UDR寄存器写入数据,触发硬件开始串行移位输出。写入后UDRE自动清零,直至发送完成再由硬件重新置位。 |

⚠️ 注意 :此函数不具备超时保护机制,在TX线路异常或外设断开时可能导致程序永久挂起。

优化建议引入——添加超时控制:

#define UART_TIMEOUT 10000

int uart_putc_timeout(uint8_t data) {

uint16_t timeout = 0;

while (!(UCSRA & (1 << UDRE))) {

if (++timeout > UART_TIMEOUT) {

return -1; // 发送失败,超时退出

}

}

UDR = data;

return 0; // 成功发送

}

UART_TIMEOUT定义最大重试次数,防止无限等待。- 返回值用于错误反馈,便于上层调用者决策重试或报警。

5.1.2 字符串批量发送函数uart_puts()封装

实际应用中常需连续发送字符串,因此需对单字节发送函数进行封装:

void uart_puts(const char *str) {

while (*str != '\0') {

uart_putc(*str++);

}

}

执行流程图(Mermaid格式):

graph TD

A[开始 uart_puts] --> B{当前字符 != '\0'?}

B -- 是 --> C[调用 uart_putc(字符)]

C --> D[指针自增]

D --> B

B -- 否 --> E[结束]

功能扩展:支持换行转换

某些终端期望 \n 换行为 \r\n ,可增强兼容性:

void uart_puts_ln(const char *str) {

while (*str) {

if (*str == '\n') {

uart_putc('\r'); // 自动插入回车

}

uart_putc(*str++);

}

}

性能瓶颈分析:

| 特性 | 描述 |

|---|---|

| CPU占用率 | 高,因每字节都需主动轮询 |

| 实时性 | 差,主程序被阻塞 |

| 可靠性 | 中等,缺乏错误恢复机制 |

| 适用场景 | 小量调试信息输出、非实时系统 |

5.1.3 发送阻塞问题与超时机制引入

如前所述,纯轮询方式存在显著缺陷: 当波特率极低或硬件故障时,CPU会长时间停滞于等待状态 ,严重影响系统整体调度能力。

为此应引入 带计数器的超时机制 ,如下表所示为不同波特率下的理论最大传输延迟估算:

| 波特率 (bps) | 每字节时间 (ms) | 假设帧长 (10位) | 最大等待时间(1000字节) |

|---|---|---|---|

| 9600 | 1.04 | 起始+8数据+停止 | ~1.04秒 |

| 19200 | 0.52 | 同上 | ~520ms |

| 115200 | 0.087 | 同上 | ~87ms |

📌 结论:即使在高速波特率下,大量数据仍可能造成数百毫秒级延迟,必须避免无限等待。

改进后的安全发送函数示例:

int uart_putc_safe(uint8_t data, uint16_t max_retries) {

uint16_t retry = 0;

while (!(UCSRA & (1 << UDRE))) {

if (++retry >= max_retries) {

return -1; // 超出重试上限

}

_delay_us(10); // 微小延时,降低CPU竞争

}

UDR = data;

return 0;

}

-

max_retries可根据波特率动态计算,例如:c #define CALC_MAX_RETRIES(baud) ((baud <= 9600) ? 1000 : 100) -

_delay_us()来自<util/delay.h>,有助于减轻总线争用。

5.2 中断驱动发送架构设计

为了克服查询方式的高CPU占用问题,采用 中断驱动发送机制 是一种高效解决方案。该方式利用 UDRIE (USART Data Register Empty Interrupt Enable)中断,在发送缓冲区空闲时由硬件触发中断服务程序(ISR),自动从缓冲区取出下一字节发送。

5.2.1 开启UDRIE中断请求

首先需使能UDRIE位以启用“数据寄存器空”中断:

// 启动UDRE中断

UCSRB |= (1 << UDRIE);

此时每当UDR发送完毕且变为空时,CPU将跳转至对应的ISR处理函数。

✅ 注意:仅当有数据需要发送时才开启UDRIE,否则会频繁触发无效中断。

5.2.2 构建发送缓冲区队列

使用环形缓冲区(Circular Buffer)管理待发数据,提升吞吐效率并减少中断频率。

环形缓冲区结构定义:

#define TX_BUFFER_SIZE 64

typedef struct {

uint8_t buffer[TX_BUFFER_SIZE];

uint8_t head; // 写入位置

uint8_t tail; // 读取位置

uint8_t count; // 当前数据量

} ring_buffer_t;

static ring_buffer_t tx_buffer = { .head = 0, .tail = 0, .count = 0 };

缓冲区操作函数:

int tx_buffer_push(uint8_t data) {

if (tx_buffer.count == TX_BUFFER_SIZE) return -1; // 满

tx_buffer.buffer[tx_buffer.head] = data;

tx_buffer.head = (tx_buffer.head + 1) % TX_BUFFER_SIZE;

tx_buffer.count++;

return 0;

}

uint8_t tx_buffer_pop() {

uint8_t data = tx_buffer.buffer[tx_buffer.tail];

tx_buffer.tail = (tx_buffer.tail + 1) % TX_BUFFER_SIZE;

tx_buffer.count--;

return data;

}

5.2.3 在ISR中自动取数并写入UDR

ISR(USART_UDRE_vect) {

if (tx_buffer.count > 0) {

// 从缓冲区取一个字节发送

UDR = tx_buffer_pop();

} else {

// 缓冲区已空,关闭UDRIE中断

UCSRB &= ~(1 << UDRIE);

}

}

逻辑详解:

| 步骤 | 操作 | 目的 |

|---|---|---|

| 1 | 判断缓冲区是否有数据 | 防止空发送 |

| 2 | UDR = tx_buffer_pop(); |

触发硬件发送,同时更新tail指针 |

| 3 | 若缓冲区空,则关闭UDRIE | 避免重复进入ISR,节省CPU资源 |

主控发送接口函数:

int uart_putc_isr(uint8_t data) {

uint8_t status = SREG; // 保存中断状态

cli(); // 关闭全局中断,保证原子操作

if (tx_buffer.count < TX_BUFFER_SIZE) {

tx_buffer_push(data);

// 如果这是第一个数据,开启UDRIE以启动中断发送链

if (tx_buffer.count == 1) {

UCSRB |= (1 << UDRIE);

}

SREG = status; // 恢复中断

return 0;

} else {

SREG = status;

return -1; // 缓冲区满

}

}

- 使用

cli()和SREG保存/恢复中断状态,确保多线程安全。 - 仅当缓冲区从空变为非空时激活UDRIE,避免冗余中断。

环形缓冲区状态转移图(Mermaid)

stateDiagram-v2

[*] --> Idle

Idle --> Filling: 数据写入

Filling --> Sending: 启动发送,开启UDRIE

Sending --> Emptying: ISR逐个发送

Emptying --> Idle: 缓冲区空,关闭UDRIE

Filling --> Overflow: 缓冲区满

Overflow --> ErrorHandling

5.3 发送性能对比与适用场景分析

选择合适的发送机制需综合考虑系统负载、实时性和资源限制等因素。以下是对两种方式的深度比较。

5.3.1 轮询 vs 中断:CPU占用率实测比较

我们设定发送1KB文本数据(约1024字节),分别在9600与115200波特率下测量CPU占用情况:

| 发送方式 | 波特率 | 数据总量 | 平均CPU占用率 | 最大阻塞时间 |

|---|---|---|---|---|

| 轮询 | 9600 | 1024B | 98% | ~1.1秒 |

| 中断 | 9600 | 1024B | 5%~8% | <10μs (ISR) |

| 轮询 | 115200 | 1024B | 85% | ~90ms |

| 中断 | 115200 | 1024B | 3%~6% | <5μs |

🔍 测量方法:使用定时器记录主循环执行周期变化,结合逻辑分析仪验证发送时间。

分析结论:

- 轮询方式严重挤占主程序运行时间,尤其在低速波特率下表现更差;

- 中断方式将发送任务“后台化”,显著释放CPU资源;

- 尽管中断本身也有开销,但由于每次仅处理一个字节且迅速返回,总体影响极小。

5.3.2 大量日志输出场景下的推荐方案

在工业监控、调试追踪等需高频输出日志的应用中, 中断+环形缓冲区 是唯一可行方案。

推荐配置参数:

| 项目 | 推荐值 |

|---|---|

| 缓冲区大小 | ≥256字节(应对突发日志) |

| 日志格式化 | 在主循环中完成,而非ISR内 |

| 错误处理 | 提供 buffer_full_callback() 钩子函数 |

| 流量控制 | 可选支持XON/XOFF协议 |

示例应用场景:

// 主循环中周期性打印传感器数据

void log_sensor_data(float temp, float humi) {

char buf[64];

snprintf(buf, sizeof(buf), "TEMP:%.2f,HUMI:%.2f\n", temp, humi);

for (int i = 0; buf[i]; i++) {

uart_putc_isr(buf[i]); // 非阻塞发送

}

}

- 所有格式化操作在主循环完成,ISR仅负责发送原始字节;

- 即使串口暂时拥堵,也不会中断主逻辑运行。

5.3.3 实时性要求高的控制系统应用建议

对于电机控制、PID调节等硬实时系统, 不应依赖串口发送作为关键路径的一部分 。

设计原则:

- 禁止在中断中执行耗时操作 ,包括浮点运算、字符串拼接;

- 优先保障控制逻辑执行周期稳定 ,串口通信降级为辅助通道;

- 采用分级日志机制 :只发送关键事件(如错误、状态变更);

- 必要时使用DMA+双缓冲(若硬件支持) ,进一步解耦CPU与通信。

推荐架构模型:

+---------------------+

| 控制主循环 |

| (固定周期,高优先级) |

+----------+----------+

|

v

+---------------------+

| 日志事件入队列 |

| (放入ring buffer) |

+----------+----------+

|

v

+---------------------+

| USART_UDRE 中断服务 |

| (逐字节发送,低延迟) |

+---------------------+

该模型实现了 控制与通信的完全解耦 ,既保证了系统实时性,又维持了必要的可观测性。

综合对比表格

| 对比维度 | 查询方式(轮询) | 中断驱动方式 |

|---|---|---|

| CPU占用 | 高(持续轮询) | 低(事件驱动) |

| 实时性 | 差(阻塞主程序) | 好(异步处理) |

| 内存开销 | 极小(无缓冲) | 中等(需缓冲区) |

| 编程复杂度 | 简单 | 较高(需同步机制) |

| 适合数据量 | ≤100字节/次 | 任意大小 |

| 抗干扰能力 | 弱(易卡死) | 强(带超时/恢复) |

| 典型用途 | 调试初期、简单回显 | 产品级、日志系统 |

综上所述,尽管查询方式易于实现,但在现代嵌入式系统中已逐渐被淘汰;而中断驱动结合环形缓冲区的架构,凭借其高效率、低延迟和良好扩展性,成为高性能串口通信的标准实践方案。开发者应根据具体需求灵活选择,并在关键系统中优先部署非阻塞通信机制,以构建稳健可靠的嵌入式应用。

6. 串口数据接收机制设计与中断服务处理

在嵌入式系统中,串行通信的可靠性与实时性高度依赖于接收端的数据采集策略。对于AVR MEGA88这类资源有限但功能完整的8位单片机而言,如何高效、稳定地捕获来自外部设备(如PC、传感器或其他微控制器)的串口数据,是构建稳健通信链路的关键环节。本章深入探讨基于MEGA88 USART模块的两种核心接收机制——轮询方式和中断驱动方式,并重点剖析中断服务程序(ISR)的设计原则、环形缓冲区的实现逻辑、错误异常处理流程以及多字节命令解析架构。通过理论推导、代码实践与性能对比,建立一套适用于工业级应用的高鲁棒性串口接收框架。

6.1 轮询方式接收实现

轮询(Polling)是最基础也是最直观的串口数据接收方法,其本质是在主循环中持续检查USART状态寄存器中的接收完成标志位RXC,一旦该位被置起,则从数据寄存器UDR中读取有效字节。尽管实现简单,但在高频率或突发性通信场景下存在明显局限。

6.1.1 检查RXC标志位获取有效数据

在MEGA88的USART0模块中, UCSRA 寄存器的第7位 RXC 用于指示是否已完成一个完整数据帧的接收。当接收到一帧数据后,硬件自动将 RXC=1 ;若软件未及时读取 UDR ,该标志保持置位,直到执行了对 UDR 的读操作为止。

因此,典型的轮询接收逻辑如下:

while (!(UCSRA & (1 << RXC))); // 等待接收完成

return UDR; // 返回接收到的数据

此段代码构成了轮询式接收的核心判断结构。它利用位操作检测 RXC 标志的状态,确保只有在有数据到达时才进行下一步操作,避免非法访问空数据寄存器。

参数说明:

UCSRA:USART控制和状态寄存器A,包含多个关键状态标志。(1 << RXC):左移运算生成对应RXC位的掩码(即0x80)。&运算符:用于提取特定标志位值。!()外层取反:使while循环持续等待直至条件成立。

注意 :必须先确认

RXC为1再读取UDR,否则可能引发不可预测行为。此外,读取UDR会自动清除RXC标志,防止重复处理同一数据。

6.1.2 函数uart_getc()返回接收到的字节

封装上述逻辑为可复用函数是工程实践中常见的做法。以下是一个标准的阻塞式接收函数示例:

#include <avr/io.h>

unsigned char uart_getc(void) {

while (!(UCSRA & (1 << RXC))) {

; // 等待数据到达

}

return UDR;

}

该函数具有良好的可移植性,适用于大多数以阻塞方式工作的轻量级应用场景,例如调试信息回显或低频配置指令接收。

逐行代码分析:

#include <avr/io.h>:引入AVR-GCC标准头文件,定义所有寄存器符号。unsigned char uart_getc(void):声明无参数、返回8位数据的函数。while (!(UCSRA & (1 << RXC))):持续查询RXC标志,构成忙等待(Busy-Wait)机制。return UDR;:一旦接收到数据,立即从UDR取出并返回。

此函数为“阻塞型”,意味着CPU在此期间无法执行其他任务,直到收到至少一个字节。

6.1.3 缺点分析:无法及时响应突发数据包

虽然轮询方式易于理解和调试,但其固有的缺陷限制了其在复杂系统中的适用范围。

| 缺点 | 描述 |

|---|---|

| CPU占用率高 | 主循环长时间陷入等待状态,浪费处理器周期 |

| 实时性差 | 若主程序正在处理耗时任务(如ADC采样),可能导致新数据覆盖旧数据 |

| 易发生溢出 | 当连续高速发送时,若未能及时读取, UDR 会被新数据覆盖,触发DOR(Data OverRun)错误 |

更严重的是,在没有中断支持的情况下,若MCU同时运行多个任务(如PWM输出、定时扫描等),则极有可能错过部分输入数据包,造成通信中断或协议解析失败。

为此,需引入更为高效的中断驱动接收机制。

6.2 基于中断的接收机制构建

为了克服轮询方式带来的效率瓶颈,现代嵌入式通信普遍采用中断驱动模型。通过使能USART接收中断,每当有数据到达时,CPU自动跳转至预设的中断服务程序(ISR),实现非阻塞、高响应的数据采集。

6.2.1 使能RXCIE接收中断

要启用接收完成中断,必须设置 UCSRB 寄存器中的 RXCIE 位(Receive Complete Interrupt Enable)。具体操作如下:

UCSRB |= (1 << RXCIE); // 使能接收中断

sei(); // 开启全局中断

其中:

- UCSRB 是USART控制和状态寄存器B,负责中断与功能使能。

- RXCIE = 1 允许当 RXC 标志置位时触发中断。

- sei() 来自 <avr/interrupt.h> ,开启全局中断允许位(I bit in SREG)。

重要提示 :必须调用

sei()才能真正激活中断系统,否则即使设置了RXCIE也不会进入ISR。

6.2.2 设计环形缓冲区(Ring Buffer)存储输入数据

由于中断服务程序应尽可能短小精悍,不能在其中直接处理复杂协议或延时操作,故通常采用“生产者-消费者”模型:ISR作为“生产者”快速将数据写入缓冲区,主循环作为“消费者”从中提取并解析。

最常用的缓冲结构是 环形缓冲区(Circular/Ring Buffer) ,具备空间利用率高、无需频繁内存移动的优点。

Ring Buffer 数据结构定义:

#define RX_BUFFER_SIZE 64

typedef struct {

unsigned char buffer[RX_BUFFER_SIZE];

volatile uint8_t head; // 写指针(ISR修改)

volatile uint8_t tail; // 读指针(主循环修改)

} ring_buffer_t;

static ring_buffer_t rx_buffer = { .head = 0, .tail = 0 };

head:由ISR更新,指向下一个待写入位置。tail:由主程序更新,指向下一个待读取位置。- 使用

volatile关键字防止编译器优化导致变量缓存。

环形缓冲区工作原理图(Mermaid 流程图):

graph LR

A[ISR 触发] --> B{是否有新数据?}

B -- 是 --> C[读取UDR]

C --> D[计算(head+1)%SIZE]

D --> E{是否满?}

E -- 否 --> F[存入buffer[head]]

F --> G[head++]

G --> H[退出ISR]

E -- 是 --> I[丢弃或报错]

I --> H

J[主循环] --> K{tail != head?}

K -- 是 --> L[取出buffer[tail]]

L --> M[tail++]

M --> N[处理数据]

K -- 否 --> O[继续循环]

该图清晰展示了中断与主程序之间的协同关系:ISR专注采集,主循环负责消费,二者通过共享缓冲区解耦。

6.2.3 在ISR中快速读取UDR并存入缓冲区

以下是完整的接收中断服务程序:

#include <avr/interrupt.h>

ISR(USART_RX_vect) {

uint8_t data = UDR;

uint8_t next_head = (rx_buffer.head + 1) % RX_BUFFER_SIZE;

if (next_head != rx_buffer.tail) { // 判断是否满

rx_buffer.buffer[rx_buffer.head] = data;

rx_buffer.head = next_head;

}

// 否则丢弃数据(可选记录溢出次数)

}

逐行逻辑分析:

ISR(USART_RX_vect):绑定到USART接收中断向量。uint8_t data = UDR;:立即读取UDR,清除RXC标志,避免后续中断遗漏。next_head = (head + 1) % SIZE:预判下一写入位置,判断是否会覆盖未读数据。if (next_head != tail):比较写指针与读指针,防止缓冲区溢出。- 成功写入后更新

head,否则丢弃数据(也可增加溢出计数器用于诊断)。

最佳实践 :禁止在ISR中调用

printf、delay_ms等阻塞性函数,以免影响系统实时性。

6.3 接收错误异常处理

在实际通信环境中,噪声干扰、波特率偏差或线路故障常导致接收错误。MEGA88提供了三种主要错误标志供检测:帧错误(FE)、数据溢出(DOR)、奇偶校验错误(UPE)。合理识别并处理这些异常,是提升通信健壮性的必要手段。

6.3.1 帧错误(FE)、数据溢出(DOR)、奇偶校验错误(UPE)判断

这些错误标志均位于 UCSRA 寄存器中:

- FE (Frame Error):第1位,表示停止位未正确检测,常见于波特率不匹配。

- DOR (Data OverRun):第3位,表示新数据到达时旧数据尚未被读取, UDR 被覆盖。

- UPE (Parity Error):第2位,仅在启用奇偶校验模式时有效。

可在ISR中扩展错误检测逻辑:

ISR(USART_RX_vect) {

uint8_t status = UCSRA;

uint8_t data = UDR;

if (status & (1 << FE)) {

/* 帧错误 */

} else if (status & (1 << DOR)) {

/* 溢出错误 */

} else if (status & (1 << UPE)) {

/* 奇偶错误 */

}

uint8_t next = (rx_buffer.head + 1) % RX_BUFFER_SIZE;

if (next != rx_buffer.tail) {

rx_buffer.buffer[rx_buffer.head] = data;

rx_buffer.head = next;

}

}

错误类型与成因对照表:

| 错误类型 | 标志位 | 可能原因 | 应对措施 |

|---|---|---|---|

| 帧错误(FE) | FE | 波特率不一致、信号衰减、起始位畸变 | 校准晶振、降低波特率、增强抗干扰 |

| 数据溢出(DOR) | DOR | 主循环处理过慢、缓冲区太小 | 扩大缓冲区、使用DMA(若有)、优化主循环 |

| 奇偶校验错误(UPE) | UPE | 传输过程受电磁干扰 | 启用重传机制、改用CRC校验 |

6.3.2 清除错误标志以恢复正常通信

值得注意的是,某些错误标志(如FE、UPE)不会因读取 UDR 而自动清除,必须通过特定顺序的操作来复位。

正确的清除流程为:

1. 先读取 UCSRA 获取状态;

2. 再读取 UDR 获取数据。

两者顺序不可颠倒!

uint8_t status = UCSRA; // 第一步:读状态

uint8_t data = UDR; // 第二步:读数据 → 自动清除错误标志

若只读 UDR 而不读 UCSRA ,则错误标志可能残留,影响后续判断。

6.3.3 日志记录与故障诊断接口预留

为便于后期调试,建议在发生错误时记录统计信息,并提供查询接口:

volatile uint32_t error_frame_count = 0;

volatile uint32_t error_overrun_count = 0;

volatile uint32_t error_parity_count = 0;

// 在ISR中增加计数

if (status & (1 << FE)) {

error_frame_count++;

} else if (status & (1 << DOR)) {

error_overrun_count++;

} else if (status & (1 << UPE)) {

error_parity_count++;

}

可通过串口命令查询这些变量,形成简易的“通信健康监测系统”。

6.4 多字节命令解析策略

在实际项目中,单字符通信已无法满足需求,往往需要接收带有协议结构的多字节报文,如“包头+长度+数据+校验和”格式。这就要求系统具备从环形缓冲区中提取完整帧的能力。

6.4.1 包头+长度+校验和协议格式设计

定义一种典型协议帧结构如下:

| 字段 | 长度(字节) | 说明 |

|---|---|---|

| Start Byte | 1 | 固定值 0xAA,标识帧开始 |

| Length | 1 | 数据域长度(N) |

| Data | N | 实际负载数据 |

| Checksum | 1 | 所有前序字节异或结果 |

优点:结构清晰、易于实现、具备基本完整性校验。

6.4.2 主循环中从缓冲区提取完整报文

主程序周期性调用解析函数,尝试从环形缓冲区中提取合法帧:

int parse_packet(unsigned char *packet, int max_len) {

static enum { WAIT_SYNC, WAIT_LEN, WAIT_DATA, WAIT_CS } state = WAIT_SYNC;

static uint8_t len = 0;

static uint8_t pos = 0;

static uint8_t cs_calc = 0;

while (rx_buffer.tail != rx_buffer.head) {

uint8_t c = rx_buffer.buffer[rx_buffer.tail];

rx_buffer.tail = (rx_buffer.tail + 1) % RX_BUFFER_SIZE;

switch (state) {

case WAIT_SYNC:

if (c == 0xAA) {

cs_calc = c;

state = WAIT_LEN;

}

break;

case WAIT_LEN:

len = c;

cs_calc ^= c;

pos = 0;

state = (len > 0) ? WAIT_DATA : WAIT_CS;

break;

case WAIT_DATA:

packet[pos++] = c;

cs_calc ^= c;

if (pos >= len) state = WAIT_CS;

break;

case WAIT_CS:

if (c == cs_calc) {

packet[len] = '\0'; // 可选添加结束符

return len; // 成功返回数据长度

} else {

state = WAIT_SYNC; // 校验失败,重新同步

}

break;

}

}

return -1; // 未收到完整帧

}

参数说明:

packet[]:用户提供的存储数组。max_len:防止越界(未在本例体现,建议加入边界检查)。- 返回值:成功则返回数据长度,失败返回-1。

逻辑流程图(Mermaid):

stateDiagram-v2

[*] --> WAIT_SYNC

WAIT_SYNC --> WAIT_LEN : 收到0xAA

WAIT_LEN --> WAIT_DATA : 收到长度字节

WAIT_DATA --> WAIT_DATA : 继续接收数据

WAIT_DATA --> WAIT_CS : 数据收完

WAIT_CS --> [*] : 校验成功 → 返回结果

WAIT_CS --> WAIT_SYNC : 校验失败

any --> WAIT_SYNC : 发生错误或超时

该状态机确保即使在数据流中断或错位情况下也能逐步恢复同步。

6.4.3 解耦接收与处理过程提升系统稳定性

将接收(ISR)、缓存(ring buffer)、解析(main loop)三者分离,形成清晰的层次化架构:

物理层接收 → ISR写入缓冲区 → 主循环提取帧 → 协议层处理

这种设计不仅提升了系统的模块化程度,还增强了容错能力。例如,即使某次校验失败,也不会影响下一条消息的正常接收。

此外,还可进一步引入超时机制(如使用定时器中断检测半帧阻塞),防止因丢失某个字节而导致永久卡死。

7. 双串口通信扩展与完整项目实例解析

7.1 MEGA88双USART资源利用策略

AVR MEGA88微控制器虽然主要以单个USART(即USART0)著称,但部分增强型号或引脚兼容的衍生芯片(如MEGA88P、MEGA168/328)支持 双UART结构 。在实际工程中,若需同时连接多个串行设备(例如PC调试终端与GPS模块),可通过外接SP330EEN等电平转换芯片或采用软件模拟方式实现多路串行通信。然而,对于具备硬件双USART的MCU(如ATmega1284P),本节所讨论的设计原则可直接迁移应用。

7.1.1 USART0与USART1独立配置原则

在支持双USART的系统中,每个通道拥有独立的寄存器空间和中断向量,其初始化必须分别进行:

// 示例:双USART波特率设置(F_CPU = 16MHz, BAUD=9600)

#define BAUD 9600

#include <util/setbaud.h>

void uart0_init() {

UBRR0H = UBRRH_VALUE;

UBRR0L = UBRRL_VALUE;

UCSR0C = _BV(UCSZ01) | _BV(UCSZ00); // 8位数据

UCSR0B = _BV(RXEN0) | _BV(TXEN0) | _BV(RXCIE0); // 使能收发+接收中断

}

void uart1_init() {

UBRR1H = UBRRH_VALUE;

UBRR1L = UBRRL_VALUE;

UCSR1C = _BV(UCSZ11) | _BV(UCSZ10);

UCSR1B = _BV(RXEN1) | _BV(TXEN1) | _BV(RXCIE1);

}

参数说明 :

-UBRRxH/L:分别为第x路USART的波特率寄存器高/低字节。

-UCSRxB中的RXENx/TXENx/RXCIEx需按通道编号启用。

- 每个USART有独立中断服务函数,如USART_RX_vect和USART1_RX_vect。

7.1.2 不同设备间通信分工设计(如PC+传感器)

典型应用场景如下表所示:

| 串口通道 | 连接目标 | 功能描述 | 数据格式 | 波特率 |

|---|---|---|---|---|

| USART0 | PC(上位机) | 接收控制命令、发送状态日志 | ASCII + 协议帧 | 115200 |

| USART1 | GPS模块 | 获取NMEA语句($GPGGA等) | NMEA-0183 | 9600 |

| USART0 | 蓝牙HC-05 | 手机APP无线透传 | 透明传输 | 38400 |

| USART1 | 温湿度传感器 | 自定义二进制协议轮询采集 | 0x02 Len Data CRC 0x03 | 19200 |

通过职责分离,避免单一串口频繁切换上下文导致的数据丢失或响应延迟。

7.2 多设备通信中的数据流管理

当多个外设共享串行链路时,需引入流量控制与调度机制保障通信完整性。

7.2.1 地址标识与路由机制引入

为区分不同目标设备,可在应用层封装地址字段。例如,在Modbus RTU风格协议中使用首字节作为设备地址:

typedef struct {

uint8_t addr; // 目标设备地址 (0x01~0xFF)

uint8_t cmd; // 命令码

uint8_t len; // 数据长度

uint8_t data[32];

uint16_t crc;

} SerialPacket;

主控程序根据 addr 字段决定是否处理该包,提升系统选择性响应能力。

7.2.2 流量控制(软件/XON-XOFF)实施

在无硬件RTS/CTS支持的情况下,可启用XON/XOFF协议:

- 当接收缓冲区剩余空间 < 10% 时,发送

0x13(XOFF) 暂停发送; - 空间恢复至 > 80% 后,发送

0x11(XON) 恢复传输。

代码示例:

if (rx_buffer_free() < RX_LOW_WATERMARK) {

uart_putc(UART0, 0x13); // 发送XOFF

} else if (rx_buffer_free() > RX_HIGH_WATERMARK) {

uart_putc(UART0, 0x11); // 发送XON

}

7.2.3 避免缓冲区溢出的主动调度算法

采用优先级队列调度任务执行顺序:

graph TD

A[新数据到达] --> B{判断来源串口}

B -->|USART0| C[放入CmdQueue]

B -->|USART1| D[放入SensorQueue]

C --> E[主循环处理命令]

D --> F[合并至环境数据池]

E --> G[生成应答包回传]

F --> H[定时汇总上传PC]

该模型解耦接收与处理流程,防止高频率数据冲击阻塞主线程。

7.3 源码文档深度解读(www.pudn.com.txt内容剖析)

假设从 PUDN 下载的开源项目文件包含以下片段:

#define UART_BAUDRATE 9600

#define ENABLE_UART1

#define DEBUG_LEVEL 2

void uart_init(void);

ISR(USART_RXC_vect) { ... }

7.3.1 文件结构与函数命名规范

该项目遵循如下组织结构:

| 文件名 | 功能 |

|---|---|

uart.c |

核心串口驱动 |

uart.h |

函数声明与宏定义 |

main.c |

主逻辑与状态机 |

ringbuf.h |

环形缓冲区模板 |

modbus_slave.c |

协议栈实现 |

函数命名采用 模块_动词 风格,如 uart_send_byte() 、 ringbuf_pop() 。

7.3.2 关键宏定义与条件编译逻辑

#ifdef ENABLE_UART1

#define PRINTF_BUF_SIZE 128

#else

#define PRINTF_BUF_SIZE 64

#endif

此类宏允许在资源受限场景下裁剪功能,提升可移植性。

7.3.3 初始化顺序与中断向量绑定细节

注意中断向量名称依赖于具体型号:

// 正确写法(ATmega88PA)

ISR(USART0_RX_vect) {

uint8_t c = UDR0;

ringbuf_put(&rx_buf, c);

}

若误用 USART_RX_vect (旧版别名),可能导致中断无法触发。

7.4 完整应用实例与调试技巧总结

7.4.1 实现MEGA88与PC双向通信的完整工程

完整初始化代码框架如下:

int main(void) {

uart0_init();

sei(); // 全局中断使能

uart_puts("System boot...\r\n");

while(1) {

char c = uart_getc();

if (c != -1) {

uart_printf("Echo: %c\r\n", c);

}

_delay_ms(10);

}

}

配合上位机串口助手发送字符,验证回显功能。

7.4.2 利用串口助手验证命令交互功能

设定一组测试命令:

| 输入命令 | 预期响应 |

|---|---|

| AT | OK |

| AT+VER | FW_V1.0 BUILD 20250401 |

| AT+TEMP | TEMP=23.5°C |

| AT+HELP | 显示帮助菜单 |

通过状态机解析输入字符串,实现简易CLI接口。

7.4.3 常见Bug排查路径:信号测量、寄存器快照、逻辑分析仪使用

建立标准化调试流程:

- 使用万用表确认TXD电平为±12V(经MAX232转换后);

- 示波器抓取波特率周期,计算误差是否超限(理想9600bps周期≈104.17μs);

- 在关键断点插入寄存器读取代码:

printf("UCSR0A=%02X, UCSR0B=%02X, UCSR0C=%02X\r\n",

UCSR0A, UCSR0B, UCSR0C);

- 使用Saleae逻辑分析仪解码UART帧,定位起始位漂移或校验错误。

此外,推荐在项目中集成“自检模式”:开机自动输出所有配置寄存器值,便于快速诊断配置失误。

简介:MEGA88单片机在工业控制、数据采集和通信系统中广泛应用,其内置的UART接口支持高效的串行通信。本文围绕MEGA88 232程序,深入讲解基于RS-232标准的串口通讯实现方法,涵盖波特率设置、寄存器配置、数据发送与接收机制,并扩展至双串口通信的应用场景。结合源码注释文件(www.pudn.com.txt),帮助开发者掌握单片机串口编程的核心技术,提升嵌入式系统开发能力。

更多推荐

已为社区贡献40条内容

已为社区贡献40条内容

所有评论(0)