STM32N647+STM32Cubemx配置详解

在以前的 STM32(如 F1/F4)中,CPU 想用哪个外设直接配置寄存器就行。但在 STM32N6 这种高性能芯片中,系统被划分为不同的信任层级(Secure 安全区、Non-Secure 非安全区)和不同的运行阶段。当前运行的代码是否有权限访问 XSPI 这个外设?

目录

PWR_EXTERNAL_SOURCE_SUPPLY (使用外部直接供电)

1. Runtime contexts (运行环境/上下文)

4. HyperBus(TM) 1.8V Inverted Clock: Port1 NCLK

5.Chip Select Override (片选覆盖): NCS1 -- Port1 --

2. 为什么选 "Application"?(外设所有权分配)

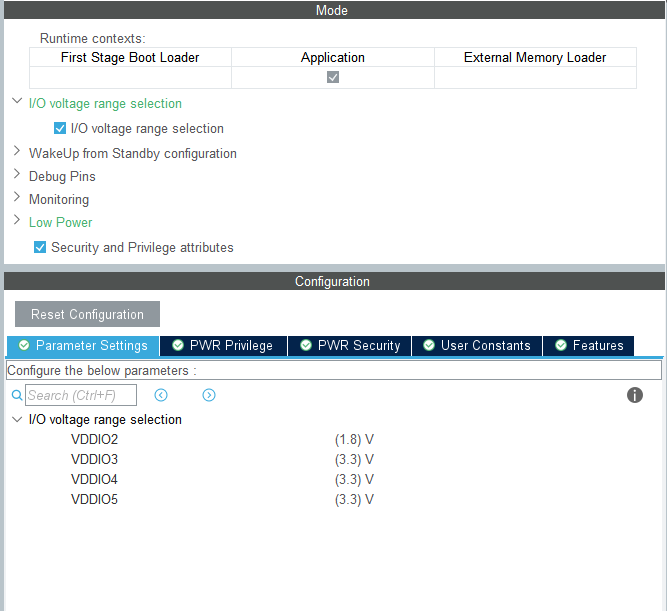

1. I/O voltage range selection (I/O 电压范围选择) —— 最重要的部分

2. Runtime contexts: Application

前言

N6不用于普通的F1 F4系列单片机,他的Cubemx配置要比那些麻烦很多,我现在将每个界面都解释一下,可能会有一点点的错误!

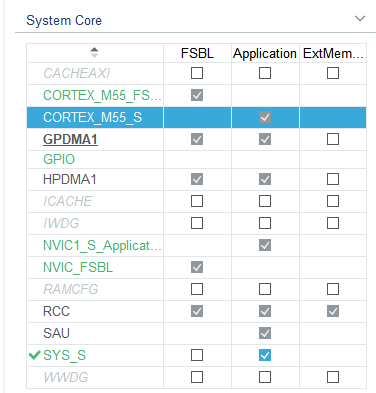

一、System Core

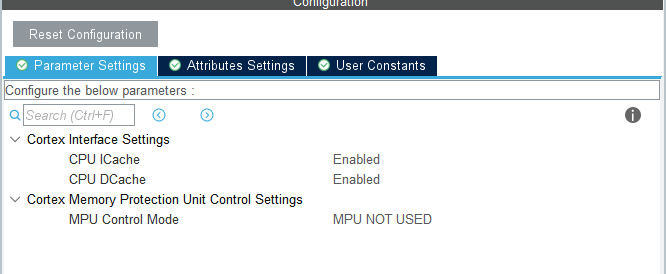

1、CORTEC_M55_S

CPU ICache DCache都要设置为Enable,主要原因是 性能需求 + Cortex-M 架构特点

1. N6 系列性能很高,必须依赖 Cache

STM32N6 使用的是 Arm Cortex‑M55 内核,主频可达 800 MHz 级别。

但 MCU 的 Flash、外部存储器速度远低于 CPU2. AXI 总线系统非常复杂

STM32N6 采用 AXI + 多级存储架构:

如果 Cache 关闭:

所有访问都走 AXI

总线负载非常大

AI / DSP / DMA 可能抢总线

3. Cortex-M55 本身就是为 Cache 设计的

Cortex-M55 是 ARM 新一代 MCU 内核(Helium/MVE 支持)。

它的设计假设:

默认启用 ICache

默认启用 DCache

否则:

SIMD / DSP / AI 运算性能会严重下降

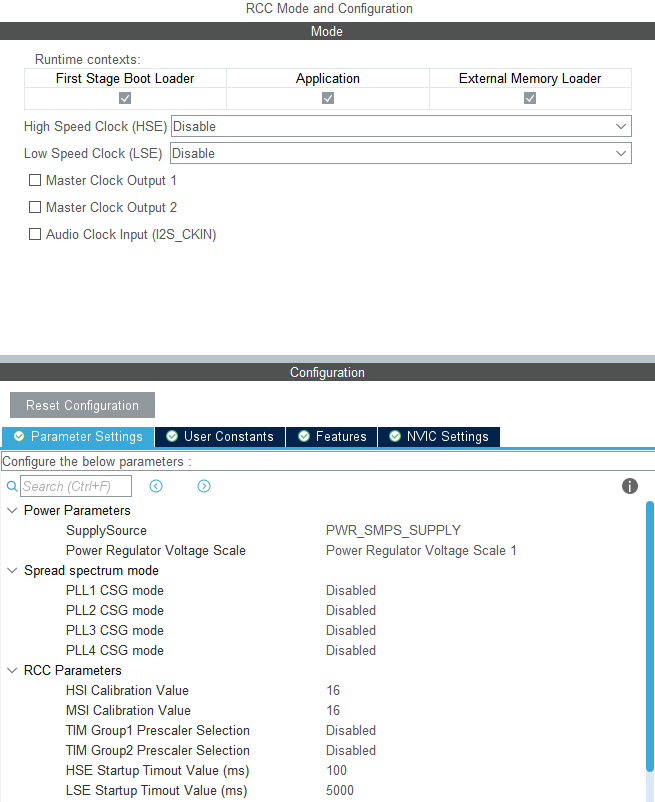

2、RCC

其中RCC (Reset and Clock Control) 界面下的 Supply Source 选项非常关键。它决定了芯片内部的 数字内核电压(Vcore) 是由什么方式提供的

PWR_SMPS_SUPPLY (使用内部开关电源)

PWR_EXTERNAL_SOURCE_SUPPLY (使用外部直接供电)

这里的“Supply Source(供电来源)”指的并不是“你的板子从哪儿通电”,而是“芯片内部的内核电压(Vcore)是怎么产生的”

为了让你彻底明白,我们把电源流向拆解开来看:

1. 外部供电(你的 Type-C 接口)

物理路径:电脑 USB (5V) -> Type-C 线 -> 板载电源芯片(如 SGM2212 或其他 LDO/DC-DC) -> VDD (3.3V)。

这个 3.3V 会送到 STM32N6 芯片的所有 VDD 引脚上。到这一步,芯片只是“通电了”,但它的“大脑”(内核)还没法工作。

2. 内核供电(CubeMX 里的选项)

STM32N6 的内核(Cortex-M55 和 NPU)不能直接用 3.3V,它们需要的是大约 1.0V - 1.1V 的低电压。

现在,这个 1.1V 怎么来?CubeMX 给出的两个选项就是在问你这件事:

选项 A:PWR_SMPS_SUPPLY (使用内部开关电源)

逻辑:芯片告诉自己:“我有 3.3V 了,我自己内部有一个高效的开关电源控制器,配合我外面引脚上接的那个电感,我可以自己把 3.3V 降压成 1.1V 给我的大脑用。”

正点原子的设计:正点原子的核心板上已经焊接了这个电感。所以,芯片可以“自给自足”。

结论:你要选这个。

选项 B:PWR_EXTERNAL_SOURCE_SUPPLY (使用外部来源供电)

逻辑:芯片认为:“虽然我有 3.3V,但我内部的降压器我不打算开。我等着我的大脑引脚(VCORE 引脚)直接从板子上其他地方飞过来一个现成的 1.1V。”

硬件要求:你的板子上必须多出一颗专门产生 1.1V 的电源芯片,并把它连到 STM32 的特定引脚上。

正点原子的设计:正点原子并没有为了内核电压专门再加一颗电源芯片,它是靠 STM32 自己降压的。

结论:如果你选这个,芯片内部的降压器不工作,内核就没有电压,你的程序一行都跑不起来,仿真器也找不到芯片。

二、Connectivity

XSPI

XSPI 是 ST 在 N6 系列上引入的最新一代 eXtended SPI 接口(可以看作是以前 QSPI 和 OctoSPI 的升级版)。

1. XSPI1、XSPI2、XSPI3 (物理控制器)

这三个是独立的硬件外设控制器(正点原子为例)。它们负责产生实际的时序信号,去和外部的存储芯片沟通。

-

XSPI2:通常用于连接主 Flash(如 Nor Flash)。由于 N6 系列内部 Flash 空间通常较小或没有,代码通常运行在外部 Flash 上(XIP,原地执行)。

-

XSPI1:通常用于连接外部 RAM(如 PSRAM 或 HyperRAM)。对于 N6 这种带 NPU 的芯片,跑模型需要大量内存,内部 SRAM 往往不够,必须挂一颗 XSPI 接口的 RAM。

-

XSPI3:备用接口,如果你需要挂第三块存储设备(或者在某些封装中引脚受限)

-

XSPIM (XSPI Manager - XSPI 管理器)

-

这是 STM32N6 的一个新特性。你可以把它理解为一个**“智能路由器”或“管脚分配矩阵”**。

-

它的作用:它坐在 XSPI 控制器和芯片引脚(GPIO)之间。它的存在是为了解决引脚复用极其复杂的问题。

-

为什么要它? 因为 N6 的引脚非常宝贵。通过 XSPIM,你可以灵活地配置:

-

让 XSPI1 走这一组引脚,XSPI2 走另一组引脚。

-

或者实现“多路复用”,比如两个控制器共享某些时钟线,但数据线分开。

-

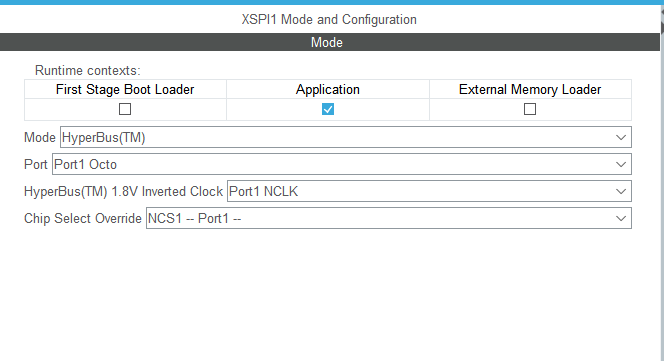

以XSPI1为例

我在cubemx中配置的是XSPI1,它对应的芯片是W958D8NBYA5I,这个应该是外设RAM,但是为什么debug模式下能实现我的功能,appli不应该烧录在flash中

区分两个概念

程序存储(Flash):

Appli代码 → 烧录在外部Flash(MX25UM25645G) → 地址 0x70100400 → CPU从这里取指令执行运行时内存(HyperRAM):

W958D8NBYA5I → 外部HyperRAM → 地址 0x90000000 → 程序运行时用来存变量、堆栈等数据为什么Debug能跑

你的链接脚本是

LRUN_RAMxspi1.ld,注意这个LRUN的含义:

- Load:代码从Flash加载

- RUN:代码在RAMxspi1(HyperRAM)中运行

所以Debug模式下:

ST-Link把代码烧到Flash └→ 启动时把代码从Flash复制到HyperRAM └→ CPU实际在HyperRAM里执行代码这就是为什么Debug模式下必须初始化XSPI1(HyperRAM),因为代码要在那里跑!

所以你CubeMX配置XSPI1是对的

只不过这个初始化在Debug模式下由Appli自己做,在Flash模式下由FSBL做,你的Appli不需要重复做

XSPI1配置

1. Runtime contexts (运行环境/上下文)

Application (你勾选了这个):这表示生成的代码将用于你的主程序

2. Mode (模式): HyperBus(TM)

Winbond (W958D) RAM 使用的是 HyperBus 协议

3. Port (端口): Port1 Octo

STM32N6 内部的 XSPI 控制器可以把信号映射到不同的引脚组(Port1 或 Port2)。

4. HyperBus(TM) 1.8V Inverted Clock: Port1 NCLK

HyperBus 协议(针对你的 W958D RAM)是差分时钟驱动的。除了一个正常的时钟信号(CLK),还需要一个反相的时钟信号(NCLK)。这里选择了 Port1 NCLK,表示开启这个反相时钟信号。这是跑 HyperRAM 的标准操作。

5.Chip Select Override (片选覆盖): NCS1 -- Port1 --

-

含义:指定使用哪一个片选引脚。

-

配置:NCS1 代表使用第 1 号片选信号线。如果一个 XSPI 接口上挂了两个芯片(很少见),你才需要区分 NCS1 和 NCS2。

三、RIF

在 STM32N6 系列中,RIF (Resource Isolation Framework,资源隔离框架) 是一个非常核心的新概念。你看到配置 XSPI 时关联到 Application,是因为 STM32N6 引入了**“多任务/多环境隔离”**的设计理念。

1. 什么是 RIF?(系统的“保安”)

在以前的 STM32(如 F1/F4)中,CPU 想用哪个外设直接配置寄存器就行。

但在 STM32N6 这种高性能芯片中,系统被划分为不同的信任层级(Secure 安全区、Non-Secure 非安全区)和不同的运行阶段。RIF 就是那个“保安”,它负责检查:当前运行的代码是否有权限访问 XSPI 这个外设?

2. 为什么选 "Application"?(外设所有权分配)

在 CubeMX 的 Runtime contexts 表格里,勾选 Application 的含义是:

-

生成初始化代码:当你勾选了 Application,CubeMX 才会把你配置的参数(比如 HyperBus 模式、频率等)生成到你的主程序代码(main.c 调用的初始化函数)中。

-

分配访问权限:RIF 会在底层配置中,把 XSPI 这个资源分配给**主应用程序(Application)**所运行的内核(通常是 Cortex-M55)。

-

如果没勾选会怎样?

-

即使你在 CubeMX 里配好了 XSPI 的参数,如果没有勾选 Application,生成的代码里可能根本没有初始化该外设的部分。

-

或者,即使你有代码,由于 RIF 没有给主程序授权,程序运行到读写 XSPI 时,会直接触发 Bus Fault(总线错误) 或 Security Violation(安全违规),导致程序死掉。

-

四、PWR

这一页是 PWR(电源管理) 的核心配置界面。对于 STM32N6 这种高性能芯片,电源配置不再仅仅是“通电”那么简单,它涉及到不同引脚组的电压适配和系统安全架构。

1. I/O voltage range selection (I/O 电压范围选择) —— 最重要的部分

这是 STM32N6 的一个关键特性。为了支持超高速的外设(比如你那颗 200MHz 的 Flash 和 RAM),芯片的引脚被分成了好几个“组”(VDDIO2, VDDIO3, VDDIO4...)。

-

VDDIO2 = (1.8) V:

-

为什么? 你之前提到的 MX25UM Flash 和 W958D RAM 在跑超高频率时,通常工作在 1.8V 逻辑电平。1.8V 相比 3.3V 信号翻转更快、功耗更低、电磁干扰更小。

-

注意:在正点原子的原理图上,VDDIO2 这一组引脚对应的硬件供电必然接的是 1.8V 的电源芯片。你必须在这里告诉软件它是 1.8V,否则芯片内部的 I/O 驱动特性(比如上升沿斜率、输入阈值)会按 3.3V 配置,导致高速通信出错甚至损坏引脚。

-

-

VDDIO3/4/5 = (3.3) V:

-

这些通常是普通的 GPIO、串口(USART)、I2C 等外设用的。正点原子的板子外部电源通常给这些组供 3.3V,所以保持默认即可。

-

2. Runtime contexts: Application

-

含义:和 XSPI 一样,勾选这个表示“生成的 main.c 应用程序有权修改电源设置”。

-

为什么要配:如果不勾选,你的程序将无法进入低功耗模式(如 Stop 或 Standby),也无法在运行时动态调整内核电压(Vcore)。

3. Low Power (低功耗设置)

-

Dead Battery Signals disabled:

-

这是 USB Type-C 的特性。如果你的板子通过 Type-C 供电,当电池完全没电时,这个信号用于特殊的电源协商。在一般的开发板(非纯电池供电产品)上,通常禁用 (Disabled) 掉,避免干扰正常的 USB 通信。

-

-

Power saving mode:

-

开启芯片内部的一些自动节电机制。对于高性能 MCU,默认开启可以降低芯片发热。

-

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)