芯片设计-利用VCS+Verdi仿真实现 8位加法器

本文介绍了使用VCS和Verdi工具进行Verilog仿真验证的完整流程。首先通过source命令设置环境变量,创建项目目录并编写8位加法器设计文件(adder_8bit.v)和测试平台(tb_adder_8bit.v)。然后使用VCS命令编译生成可执行文件simv,运行仿真验证加法器功能。最后通过Verdi工具查看波形文件(wave.fsdb),分析信号时序关系。整个过程涵盖了从环境配置、代码编

1.初始化

1.设置环境变量:

这是最重要的一步,否则系统找不到VCS命令。

# 使用 source 命令加载 VCS 和 Verdi 的环境设置脚本

# 请根据你虚拟机中的实际安装路径修改 /tools/synopsys/

source /tools/synopsys/vcs/setup.vcs

source /tools/synopsys/verdi/setup.verdi验证是否成功:执行后,立刻输入以下命令验证工具是否就绪:

bash

# 查看VCS版本

vcs -id

# 查看Verdi版本

verdi -version2.创建项目目录:

保持工作区整洁。

bash

mkdir vcs_adder_example

cd vcs_adder_example2. 编写Verilog代码

你需要创建两个文件:设计文件和测试平台文件。

设计文件:8位加法器 (adder_8bit.v)。这是一个纯粹的组合逻辑电路。

bash

vim adder_8bit.v这里要用到vim 文本编辑器,使用方法如下:

Linux vi/vim | 菜鸟教程

将以下代码粘贴进去:

verilog

`timescale 1ns/1ps

module adder_8bit (

input [7:0] a,

input [7:0] b,

input cin, // 低位进位输入

output [7:0] sum,

output cout // 进位输出

);

// 直接使用 + 运算符,综合工具会自动将其映射为加法器电路

assign {cout, sum} = a + b + cin;

endmodule测试平台文件 (tb_adder_8bit.v)。它的任务是实例化被测试的设计,并提供激励(输入信号),观察并报告输出。

bash

vim tb_adder_8bit.v将以下代码粘贴进去:

verilog

`timescale 1ns/1ps // 定义仿真时间单位/精度

module tb_adder_8bit;

// 定义连接到被测试模块的信号

reg [7:0] a;

reg [7:0] b;

reg cin;

wire [7:0] sum;

wire cout;

// 实例化被测试的8位加法器,将测试平台的信号连接到它的端口上

adder_8bit u_adder (

.a(a),

.b(b),

.cin(cin),

.sum(sum),

.cout(cout)

);

// 初始化:在仿真开始时设置初始值

initial begin

a = 8‘h00;

b = 8‘h00;

cin = 1’b0;

#100; // 等待100个时间单位

$display("Simulation started at time %0t", $time);

end

// 生成测试激励:每隔一段时间改变输入信号

initial begin

// 测试用例 1: 基本加法

#20;

a = 8‘h12;

b = 8‘h34;

cin = 1’b0;

#20;

$display(“[%0t] a=%h, b=%h, cin=%b -> sum=%h, cout=%b”, $time, a, b, cin, sum, cout);

// 测试用例 2: 测试进位

#20;

a = 8‘hFF;

b = 8‘h01;

cin = 1’b0;

#20;

$display(“[%0t] a=%h, b=%h, cin=%b -> sum=%h, cout=%b”, $time, a, b, cin, sum, cout);

// 测试用例 3: 带进位输入

#20;

a = 8‘hF0;

b = 8‘h0F;

cin = 1’b1;

#20;

$display(“[%0t] a=%h, b=%h, cin=%b -> sum=%h, cout=%b”, $time, a, b, cin, sum, cout);

// 结束仿真

#100;

$display(“Simulation finished at time %0t”, $time);

$finish; // 结束仿真进程

end

// 可选:生成波形记录文件,供Verdi或其他波形查看器使用

initial begin

$fsdbDumpfile(“wave.fsdb”); // 指定波形文件名为 wave.fsdb

$fsdbDumpvars(0, tb_adder_8bit); // 记录当前模块及其下所有子模块的信号

end

endmodule3. 使用VCS进行编译与仿真

现在进入核心环节,在终端中输入命令:

编译:VCS会将你的设计文件和测试平台一起编译成一个可执行的仿真程序 simv。

bash

# 基本命令:vcs [选项] 源文件

vcs -full64 \ # 使用64位模式

-sverilog \ # 支持SystemVerilog语法(我们的testbench是简单的SV)

-debug_access+all \ # 开启所有调试功能,为查看波形做准备

+v2k \ # 支持Verilog-2001标准

adder_8bit.v \

tb_adder_8bit.v或者

vcs -full64 -sverilog -debug_access+all +v2k adder_8bit.v tb_adder_8bit.v -o simv如果一切顺利,编译成功后当前目录下会生成 simv 可执行文件。

注意:我这里编译时失败,打开tb测试文件发现有乱码,这时可以删除掉tb文件,重新复制

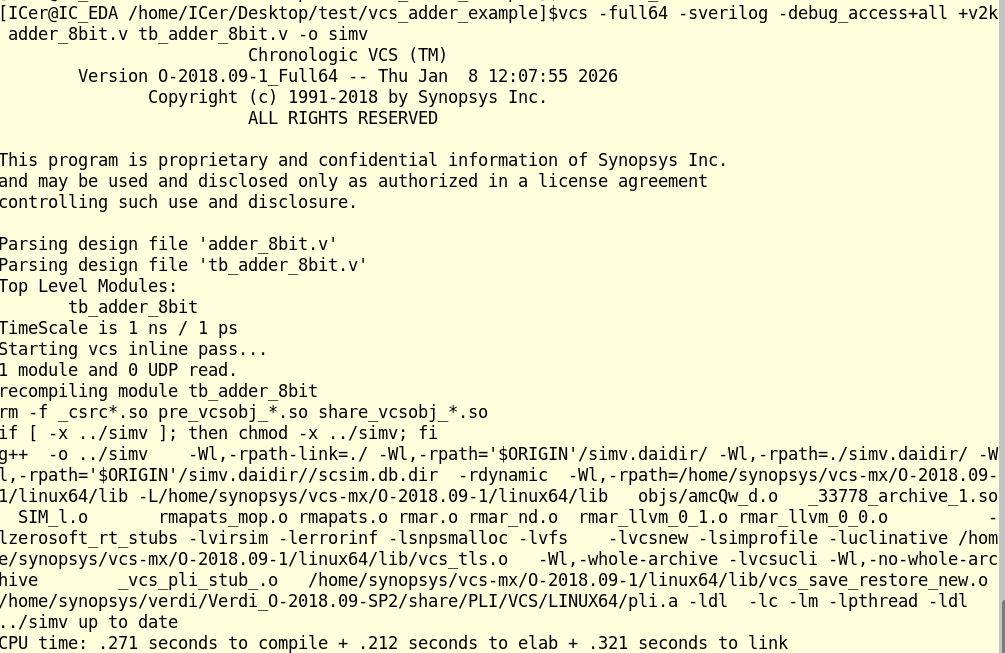

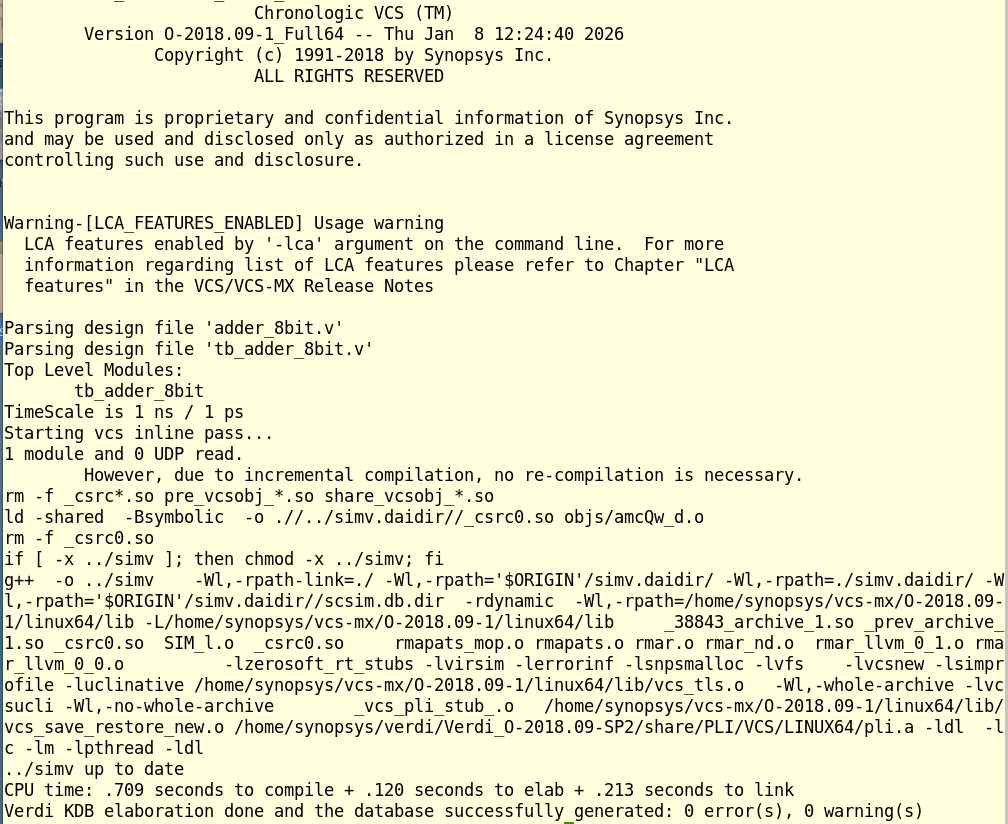

编译成功:

运行仿真:执行 simv 程序。

bash

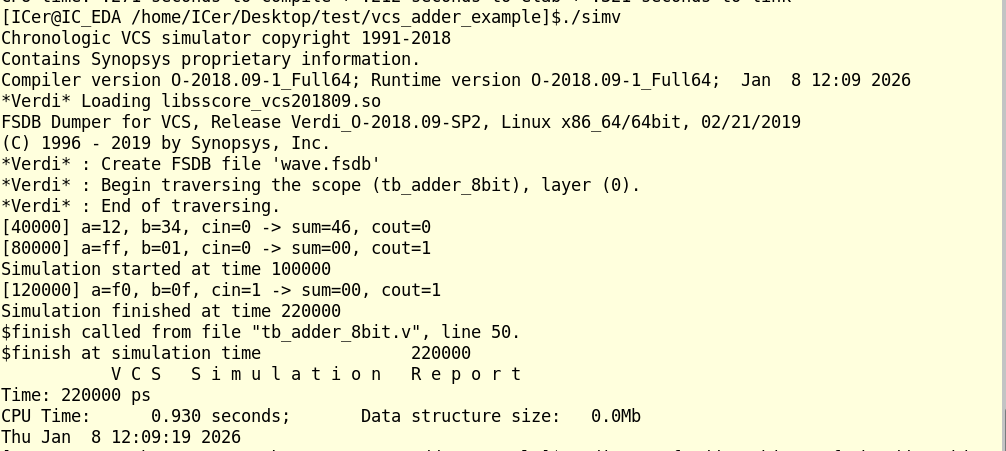

./simv仿真运行时,测试平台中的 $display 语句会将结果打印在终端上。你应该能看到类似这样的输出:

text

Simulation started at time 100

[140] a=12, b=34, cin=0 -> sum=46, cout=0

[180] a=ff, b=01, cin=0 -> sum=00, cout=1

[220] a=f0, b=0f, cin=1 -> sum=00, cout=1

Simulation finished at time 320

这表明加法器的逻辑功能是正确的(例如 0x12 + 0x34 = 0x46, 0xFF + 0x01 产生进位 cout=1,和为 0x00)。

4. 查看波形(使用Verdi)

仿真的终端输出是好的,但还需查看波形。我们在测试平台中已经通过 $fsdbDumpvars 命令生成了 wave.fsdb 波形文件。

使用Verdi打开波形:

bash

verdi -sv \ # 支持SystemVerilog

-f adder_8bit.v \ # 加入设计文件列表

-f tb_adder_8bit.v \ # 加入测试平台文件列表

-ssf wave.fsdb & # 指定要打开的波形文件,&表示后台运行或者

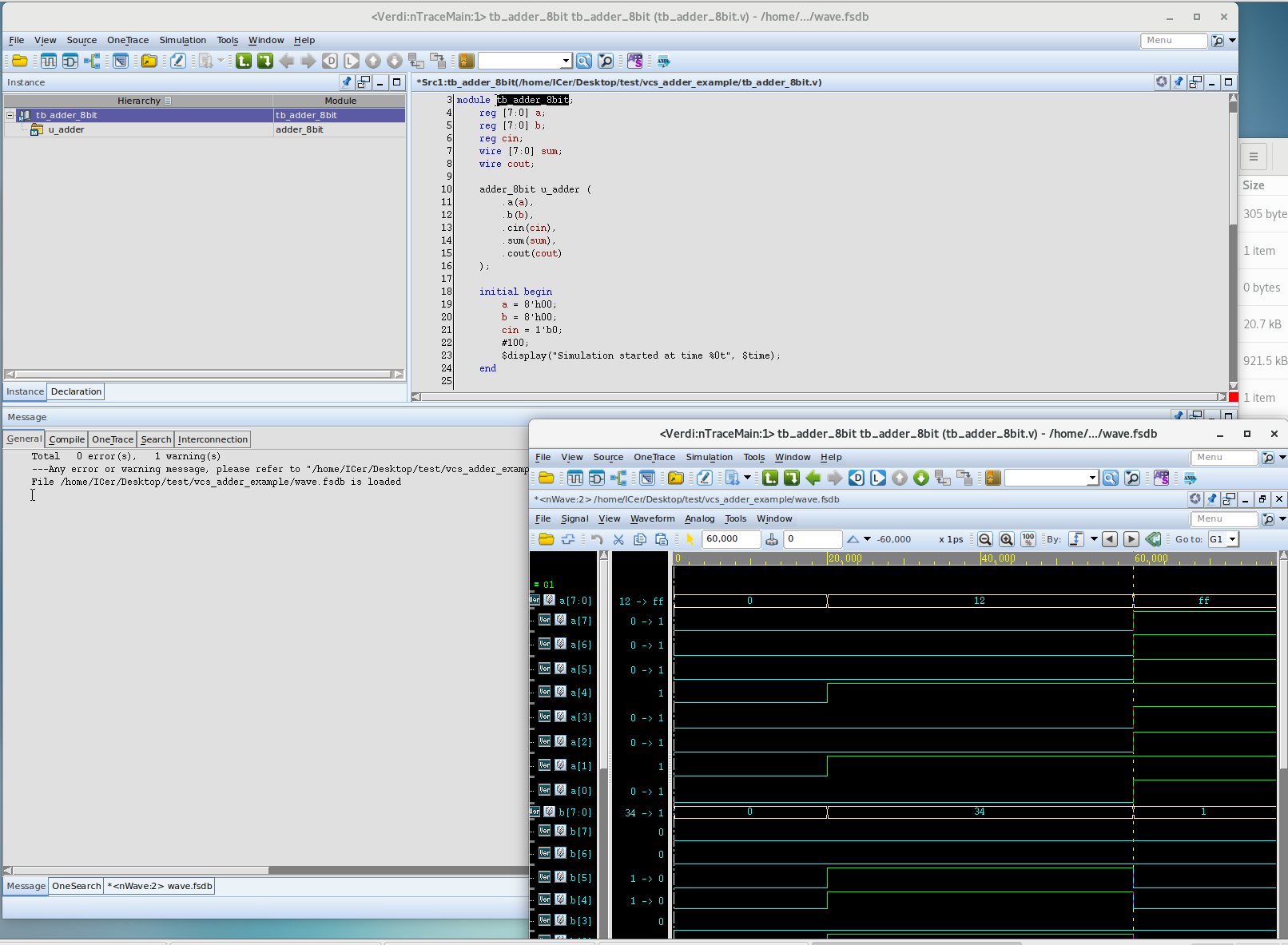

verdi -elab simv.daidir/kdb -ssf wave.fsdb &弹出verdi,左上是模型包含的文件,右上是tb_adder_8bit的文件内容

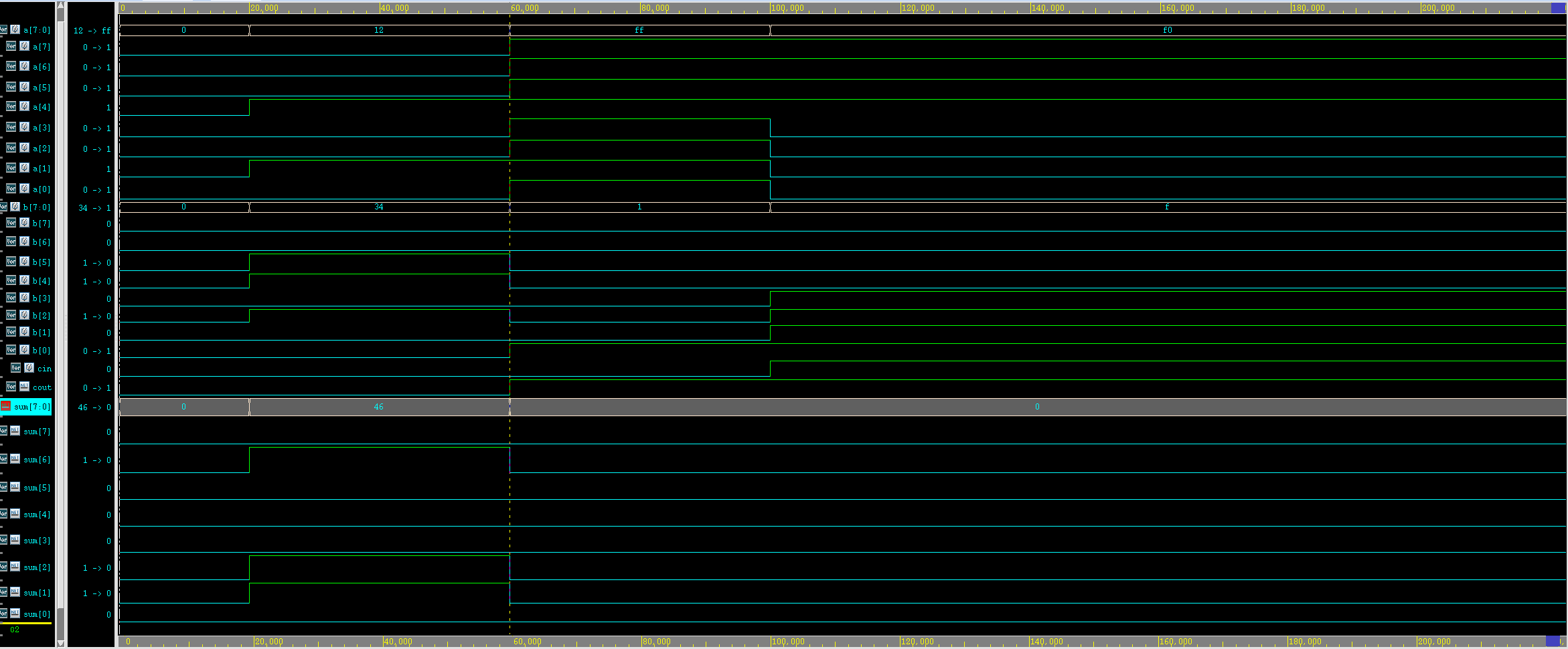

下方波形处,单击signal ,选择get signals 选择需要展示的信号,左侧信号可以拖动改变其上下所占空间

verdi 输出波形图

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)