SPI协议

SPI 协议是 Motorola 公司推出的一种同步串行接口技术,是一种高速的,全双工,同步的通信总线。寻址控制:一主多从时确保 SS 线互斥选通,同一时刻仅选中一个从机;时序匹配:严格按从机手册配置 CPOL/CPHA,避免因采样边沿错误导致数据传输失败。

目录

一、SPI 协议简介

1. 协议起源与核心定位

SPI 协议是 Motorola 公司推出的一种同步串行接口技术,是一种高速的,全双工,同步的通信总线。

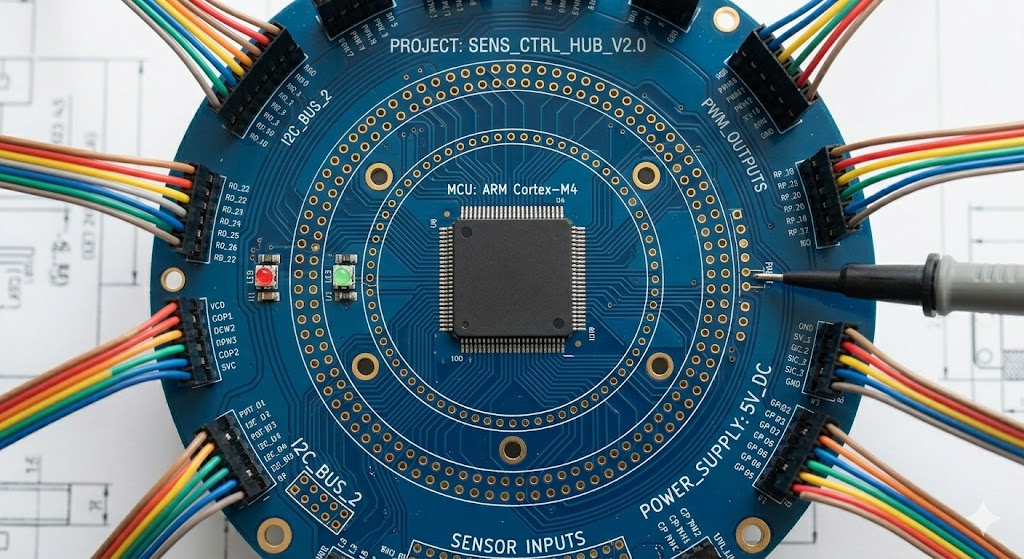

2. SPI总线拓扑结构

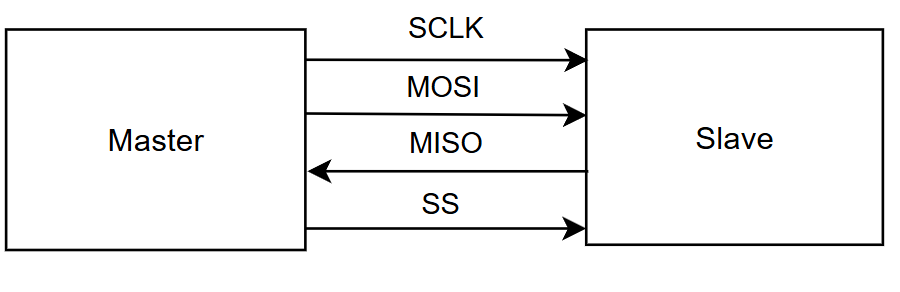

核心信号线:

- SCK(Serial Clock):串行时钟线,由主设备生成,是数据传输的 “节拍器”;

- MOSI(Master Output Slave Input):主出从入线,主设备向从设备发送数据;

- MISO(Master Input Slave Output):主入从出线,从设备向主设备返回数据;

- SS(Slave Select):片选线,主设备通过电平控制选中目标从机(也常称 CS)。

拓扑规则:

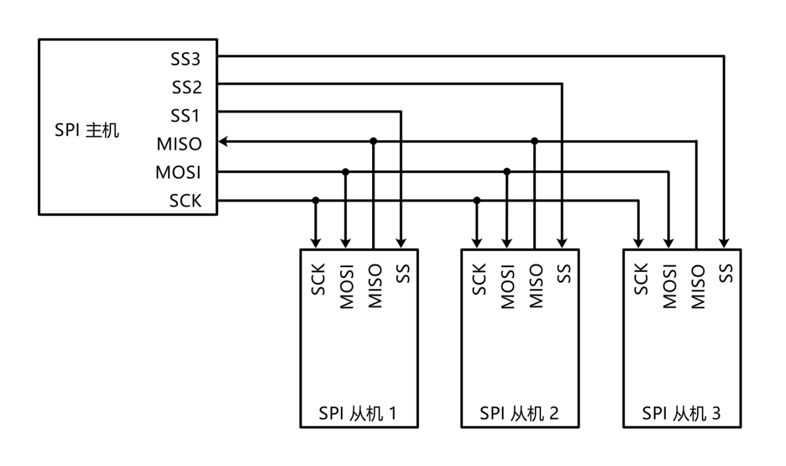

- 支持总线挂载多设备(一主多从),所有从机的 SCK、MOSI、MISO 需共接(共享总线),仅 SS 线独立;

- 硬件配置:输出引脚(SCK、MOSI)配置为推挽输出,输入引脚(MISO)配置为浮空或上拉输入;

- 特殊说明:SPI 一主一从场景下,理论上可省 SS 线,但部分从机(如 W25Q64)强制要求 SS 参与通信,建议仍用 GPIO 控制 SS(或接固定有效电平),避免从机无响应。

3.寻址方式

所有SPI设备的SCK、MOSI、MISO分别连在一起

主机另外引出多条SS控制线,分别接到各从机的SS引脚

输出引脚配置为推挽输出,输入引脚配置为浮空或上拉输入

注:SPI如果一主一从,则只需要三根线即可,片选线可以不使用

SPI一主多从通信时,通过SS片选线来区分主机和哪几个从机进行通信,只需要主机将要和从机通信的SS电平拉低即可

关键避坑:一主多从通信时,同一时刻仅能拉低 1 根 SS 线(避免多个从机的 MISO 线冲突);通信结束后需立即拉高 SS,释放从机。

二、SPI通信时序

1.移位示意图

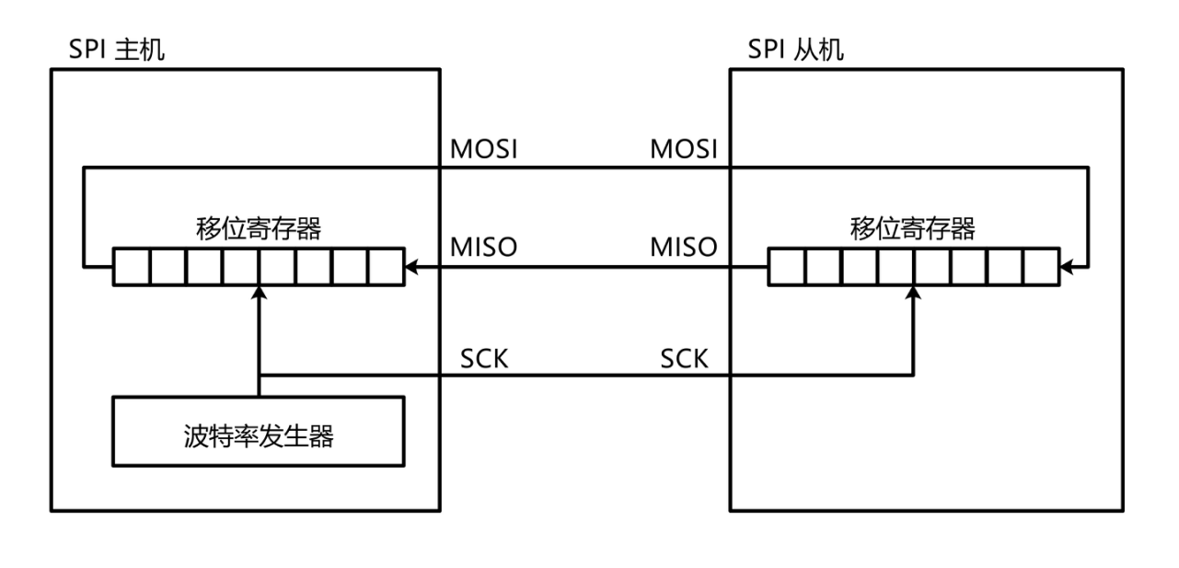

SPI 主设备和从设备内部各有一个 8 位串行移位寄存器,通信时两个寄存器通过 MOSI 和 MISO 线 “首尾相连”,形成 16 位环形结构:

- 主设备向自身 SPI 串行寄存器写入 1 字节数据,即可发起一次传输;

- 在 SCK 时钟驱动下,主从寄存器同步移位:每 1 个 SCK 周期,主从各移出 1 位数据到对应数据线(主机→MOSI、从机→MISO),同时移入对方的 1 位数据;

- 8 个 SCK 周期完成 1 字节数据交换(SPI 通信本质是 “数据交换”,主设备发数据的同时必然接收从机数据)。

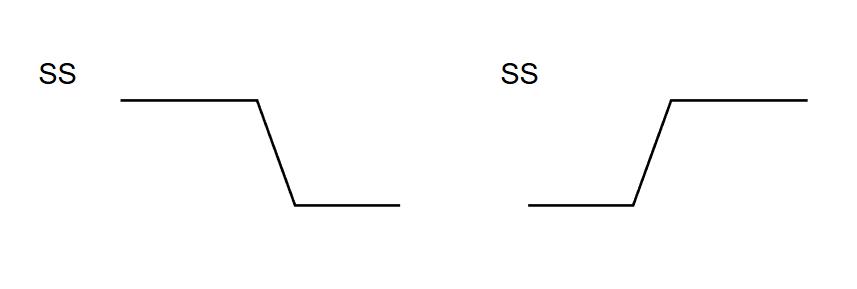

2.SPI的基本时序单元

起始条件:SS从高电平切换到低电平

终止条件:SS从低电平切换到高电平

3.交换一个字节

极性和相位

SPI 总线有四种不同的工作模式,取决于极性 (CPOL) 和相位 (CPHA) 这两个因素

极性(CPOL):表示 SCLK 空闲时的状态

- CPOL=0,空闲时 SCLK 为低电平

- CPOL=1,空闲时 SCLK 为高电平

相位(CPHA):表示采样时刻

- CPHA=0,每个周期的第一个时钟沿采样

- CPHA=1,每个周期的第二个时钟沿采样

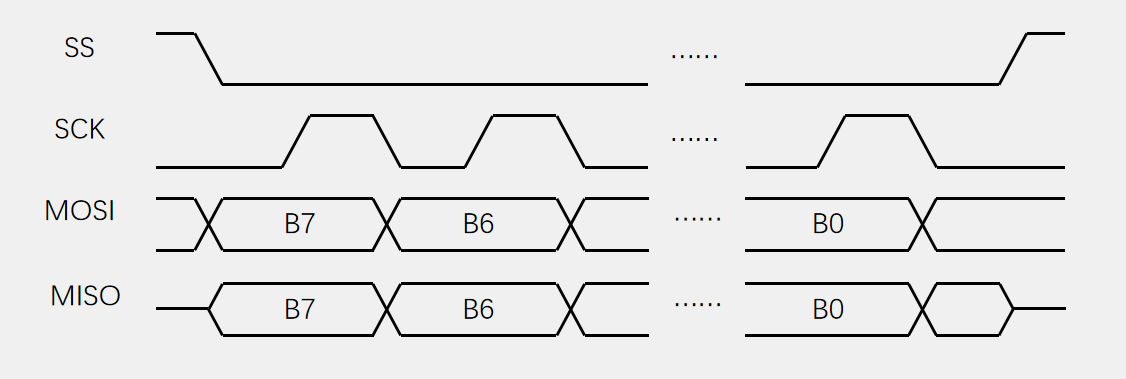

模式0:

CPOL=0:空闲状态时,SCK为低电平

CPHA=0:SCK第一个边沿移入数据,第二个边沿移出数据

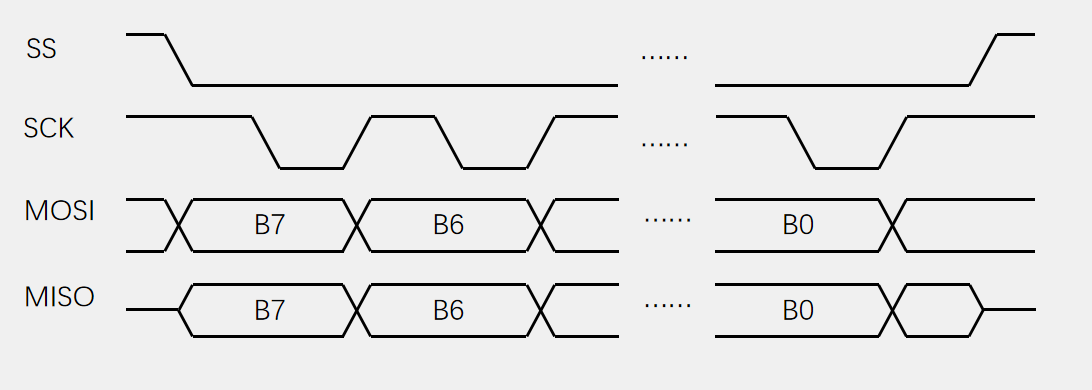

模式1:

CPOL=0:空闲状态时,SCK为低电平

CPHA=1:SCK第一个边沿移出数据,第二个边沿移入数据

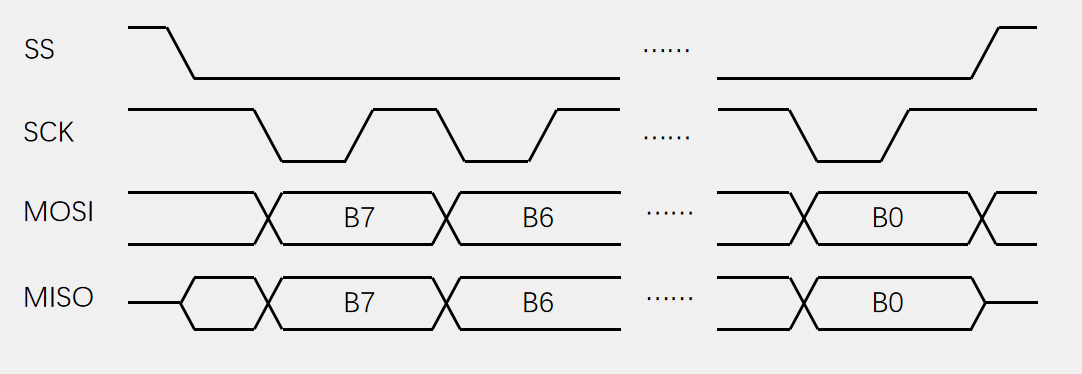

模式2:

CPOL=1:空闲状态时,SCK为高电平

CPHA=0:SCK第一个边沿移入数据,第二个边沿移出数据

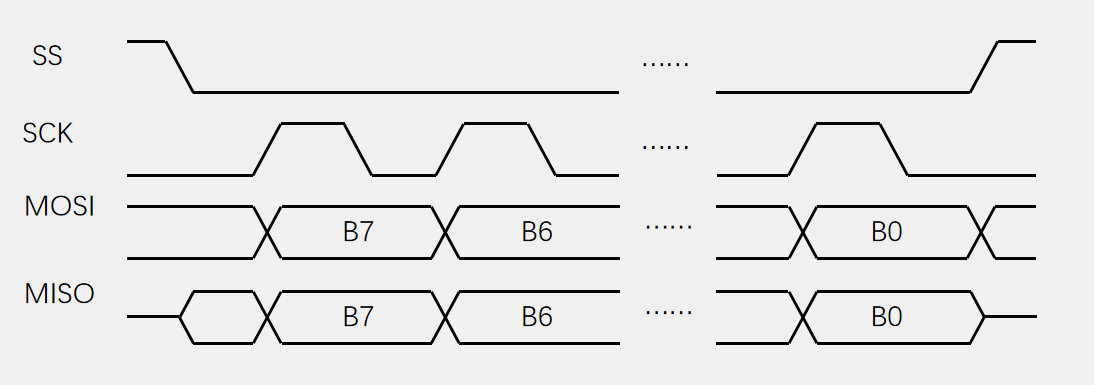

模式3:

CPOL=1:空闲状态时,SCK为高电平

CPHA=1:SCK第一个边沿移出数据,第二个边沿移入数据

三、SPI与IIC的对比

总结

SPI 的核心优势是 “高速全双工 + 硬件简单”,掌握它的关键在于两点:

- 寻址控制:一主多从时确保 SS 线互斥选通,同一时刻仅选中一个从机;

- 时序匹配:严格按从机手册配置 CPOL/CPHA,避免因采样边沿错误导致数据传输失败。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)