MOS管加下拉电阻的原因深度解析

综上,MOS管栅极添加下拉电阻,绝非可有可无的“装饰性元件”,而是基于MOS管高输入阻抗、栅极电荷敏感等核心特性,针对电路可靠性、器件安全性、抗干扰能力提出的关键设计。其核心作用是解决栅极悬空问题,确保无驱动信号时MOS管稳定关断;同时承担着泄放栅极电荷、抑制高频振荡、防护静电、保障上电安全等多重使命,是满足功能安全与电磁兼容标准的基础要素。在工程实践中,下拉电阻的选型与布局,直接体现了工程师对M

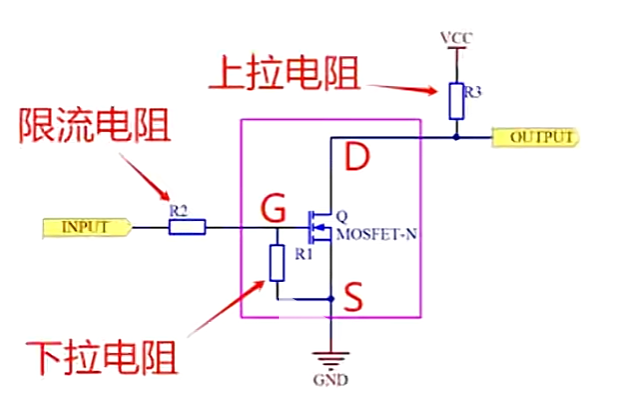

在电子电路设计中,MOS管(金属-氧化物-半导体场效应晶体管)作为核心的开关与放大器件,广泛应用于电源管理、电机驱动、DC-DC转换、微控制器外围电路等诸多场景。不少初学者在设计MOS管电路时,常会疑惑为何需在栅极添加下拉电阻——看似多余的一个元件,实则是保障电路稳定、器件安全、系统可靠的关键设计,其作用背后深度关联MOS管的物理特性、电路鲁棒性及工程实践需求。本文将从核心原理出发,结合实际应用场景,全面解析MOS管加下拉电阻的四大核心原因,同时澄清常见认知误区,为电路设计提供实用参考。

一、核心原因:解决栅极悬空问题,避免电平不确定

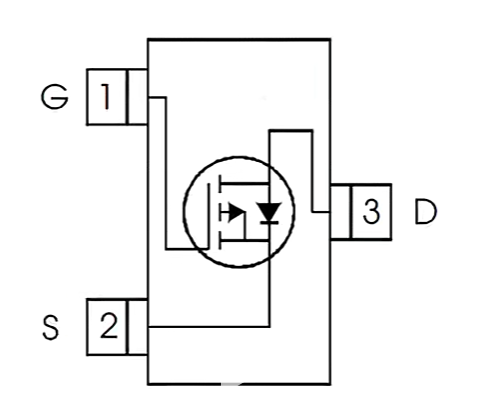

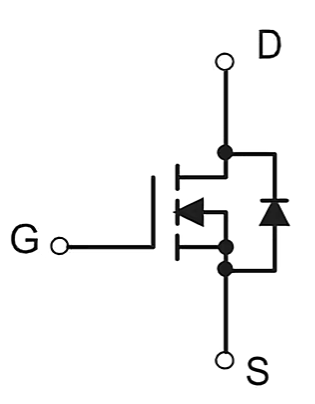

MOS管与双极型晶体管(BJT)的核心区别的之一,是其属于电压控制型器件,导通与关断完全取决于栅源电压V是否超过阈值电压V,且其栅极由一层极薄的二氧化硅绝缘层隔离,输入阻抗极高,可达10~10Ω,近乎开路状态。这种高阻抗特性使得栅极对电荷极其敏感,而下拉电阻的核心作用,就是解决栅极悬空带来的电平不确定问题。

当MOS管栅极未连接下拉电阻且无驱动信号时,栅极会处于悬空状态,形成高阻抗浮空节点。此时,微弱的静电、空间电磁耦合噪声、PCB走线的天线效应,甚至人体接触产生的静电,都可能在栅极积累电荷,导致栅源电压V随机波动,甚至超过阈值电压V。这种情况下,MOS管会处于不确定的导通与关断状态,引发一系列问题:轻则导致负载误动作、电路逻辑紊乱,重则使MOS管反复导通关断,产生大量开关噪声、功耗异常升高,甚至因长期处于半导通状态引发热失控,烧毁MOS管及后级电路。

下拉电阻的存在,相当于为栅极提供了一条可控的、低阻抗的直流泄放通路,将无驱动信号时的栅极电位强制钳位至参考地电平(GND),确保V=0V,使MOS管稳定处于关断状态,从根源上消除栅极悬空的风险。这就像给悬空的栅极“拴上安全绳”,避免其因外界干扰而“失控”,是MOS管电路可靠工作的基础保障。

二、关键作用:泄放栅极电荷,保障快速可靠关断

MOS管的栅极与源极之间存在寄生电容C(输入电容),其容量通常为数百pF至数nF。在MOS管导通过程中,栅极会积累大量电荷,使V维持在导通阈值以上;而当驱动信号消失时,若没有泄放通路,这些积累在寄生电容上的电荷无法快速释放,会导致MOS管关断延迟,甚至长时间无法关断。

下拉电阻恰好为栅极寄生电容提供了高效的泄放路径,使电容上的电荷能够通过电阻快速流入地,缩短MOS管的关断时间,确保MOS管在驱动信号撤销后迅速、可靠地关断。尤其在高频开关场景中,关断延迟过大会导致MOS管停留在半导通状态的时间延长,导通损耗急剧增加,同时可能引发桥臂直通等致命故障——例如在半桥或全桥拓扑中,若一侧MOS管关断延迟,会与另一侧导通的MOS管形成短路,电流瞬间攀升至数千安培,导致MOS管瞬间炸裂、驱动芯片损坏。

此外,在桥式拓扑中,对管开通时产生的dV/dt会通过寄生电容C耦合到本管栅极,形成米勒电流。若无下拉电阻,米勒电流无法泄放,会导致栅极电压抬升,引发MOS管误导通,而下拉电阻可有效泄放米勒电流,避免此类风险。根据工程实践经验,下拉电阻与栅极电容构成的RC时间常数τ=R×C,需控制在开关周期的1/10以内,才能确保关断延迟不会影响电路正常工作。

三、辅助作用:抑制高频振荡,提升电路抗干扰能力

MOS管的栅极、源极、漏极之间存在寄生电容(C、C),同时PCB走线会引入寄生电感,这些寄生元件会构成LC谐振回路。在无下拉电阻的情况下,该LC回路的Q值极高,易在MOS管开关瞬态激发100MHz以上的高频振荡,引发一系列问题:

一是栅极振铃幅度可达5-10V,超过MOS管栅源极最大耐压(通常为±20V),容易导致栅氧化层击穿,永久损坏MOS管;二是振铃信号若在阈值电压V附近来回穿越,会造成MOS管反复导通关断,产生巨大的开关损耗,瞬时功耗可达数百瓦,引发器件过热;三是高频振荡会产生强烈的电磁辐射,导致电路EMI(电磁干扰)超标,使产品无法通过CE、FCC等认证。

下拉电阻作为LC谐振回路的并联阻尼电阻,能够降低回路Q值,消耗振荡能量,将栅极振铃幅度抑制在2V以内,有效抑制高频振荡。同时,下拉电阻与栅极电容共同构成RC低通滤波器,可过滤沿栅极引入的高频开关噪声,进一步提升电路的抗干扰能力,尤其在工业电机、变频器等强干扰环境中,这一作用更为关键。

四、额外保障:静电防护与上电复位,降低失效风险

MOS管的栅氧化层极薄,耐压能力较弱,典型栅源最大耐压仅为±20V,而静电电荷的电压往往可达数千伏甚至上万伏,极易击穿栅氧化层,导致MOS管永久失效。在栅极悬空时,静电电荷无法泄放,会在栅极不断积累,形成高电压,进而击穿栅氧化层;而下拉电阻为静电电荷提供了安全的泄放路径,可将栅极电压限制在安全范围内,相当于为MOS管栅极提供了一道低成本、高效益的静电防护屏障,降低静电击穿的概率。

此外,在系统上电复位期间,驱动电路(如MCU GPIO)可能尚未建立稳定的输出电平,处于高阻态。此时,下拉电阻可确保MOS管栅极被钳位在低电平,使MOS管处于安全的关断状态,避免系统启动瞬间出现电源短路、负载突启等危险工况。例如在电源管理电路中,若上电时MOS管误导通,会导致电源瞬间短路,触发电源保护,甚至烧毁电源模块和MOS管,而下拉电阻可有效避免此类上电故障。

五、常见认知误区澄清与选型要点

(一)常见误区

1. 误区一:“只要驱动信号稳定,就可以省略下拉电阻”——即使驱动信号正常,当驱动电路故障(如PWM控制器死机)、PCB走线虚焊或断裂时,栅极仍可能悬空,引发误导通,下拉电阻是冗余保护的关键;

2. 误区二:“下拉电阻阻值越小越好”——阻值过小(如1kΩ以下)虽能加快电荷泄放和振荡抑制,但会显著增加静态功耗(P=V²/R),同时加重前级驱动电路的负载负担;

3. 误区三:“所有MOS管都需要加下拉电阻”——PMOS高端驱动中,通常采用上拉电阻而非下拉电阻;推挽式栅极驱动电路中,上下拉电阻协同工作,实现更快速的边沿控制;若驱动电路本身已提供可靠的低电平泄放路径(如OC门输出),可酌情省略,但工程中为提升可靠性,通常仍会保留。

(二)选型要点

下拉电阻的阻值需在泄放速度、静态功耗、抗干扰能力之间寻求平衡,典型取值范围为10kΩ~1MΩ,具体选型需结合应用场景:

1. 强干扰环境(如工业电机、变频器):优先选用1kΩ~4.7kΩ较低阻值,提升干扰响应速度,增强静电泄放能力;

2. 微功耗设备(如IoT传感器、穿戴设备):可选择47kΩ~100kΩ,降低静态功耗,需确保驱动芯片拉电流能力≥0.1mA,且开关频率低于10kHz;

3. 高速开关场景(如DC-DC变换器):需满足RC时间常数<开关周期1/10,通常选用1kΩ~20kΩ,必要时并联加速二极管,进一步缩短关断延迟;

4. 布局要求:下拉电阻需紧贴MOS管栅极引脚放置,距离<5mm,避免过长走线引入寄生电感,削弱阻尼和泄放效果,电阻功率通常选用1/8W或1/4W即可满足需求。

六、总结

综上,MOS管栅极添加下拉电阻,绝非可有可无的“装饰性元件”,而是基于MOS管高输入阻抗、栅极电荷敏感等核心特性,针对电路可靠性、器件安全性、抗干扰能力提出的关键设计。其核心作用是解决栅极悬空问题,确保无驱动信号时MOS管稳定关断;同时承担着泄放栅极电荷、抑制高频振荡、防护静电、保障上电安全等多重使命,是满足功能安全与电磁兼容标准的基础要素。

在工程实践中,下拉电阻的选型与布局,直接体现了工程师对MOS管物理机制、电路失效模式的理解深度。正确选用下拉电阻,既能避免误导通、炸管、EMI超标等常见故障,也能提升电路的稳定性和使用寿命,是电子电路设计中不可或缺的基础技巧。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)