认识MIPI:设备内部的“高速公路系统”

MIPI是移动设备内部的高速数据传输标准,主要用于连接摄像头(CSI)和显示屏(DSI)。其核心是D-PHY物理层,采用差分信号传输,包含1条时钟通道和1-4条数据通道,可在高速模式(数据传输)和低功耗模式(控制指令)间智能切换。带宽取决于通道数量和单通道速率(如1.5Gbps×2通道=3Gbps)。PCB设计需注意:阻抗匹配(100Ω差分)、等长布线(对内<6mil)、远离干扰源、最小化过

核心思想:先建立直观模型

忘记那些复杂的协议层。你可以把MIPI想象成你手机或平板电脑内部修建的一套“高速公路系统”。

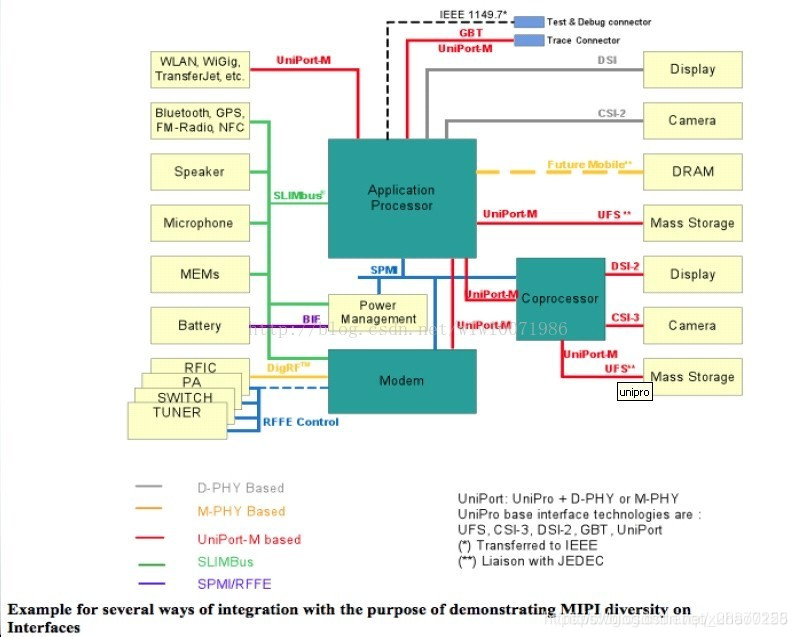

MIPI(移动行业处理器接口)是专为移动设备(如智能手机、平板电脑、笔记本电脑和混合设备)设计的行业规范的标准定义。其常见的通用的唯一物理(PHY)层,即MIPID-PHY和C-PHY。

这套系统专门负责快速运输两种最重要的“货物”:

图像:从摄像头运到处理器

MIPIC-PHY:C-PHY没有同步时钟,时钟是嵌套在数据中,通过带宽受限通道来实现高吞吐量性能,例如将显示器和摄像头连接到应用处理器。它可为MIPI相机串行接口(MIPICSI-2)和MIPI显示接口(MIPLDSI-2)生态系统提供PHY,帮助设计人员扩展其实现,以支持各种更高分辨率的图像传感器和显示器

画面:从处理器运到屏幕。

MIPI D-PHY:更常用于智能手机的相机和显示屏,因为它具有灵活、高速、低功耗和低成本的特点。提供了对DSI(串行显示接口)和CSI(串行摄像头接口)在物理层上的定义,采用一个差分时钟和1-4对差分数据线来传输数据。

整个系统如何工作,就是“如何规划一条高效、省电的高速公路来运货”的过程。

第一阶段:MIPI是什么?—— 一套“交通标准”

MIPI不是一个具体的硬件插槽(像USB口那样),而是一套国际公认的“交通建设与运输标准”。

目的:在手机、平板、汽车等设备内部,把各个零件(摄像头、屏幕、传感器)连接起来。

好处:大家(芯片厂、屏幕厂、摄像头厂)都按同一个标准来“修路”和“造车”,设备厂家(比如手机品牌)就能像搭积木一样,灵活选择最好的摄像头、最好的屏幕,组合成一台好设备,而不用担心它们之间“连不上”或“沟通不畅”。

核心理念:高速、低功耗、节省空间。

一句话概括:MIPI是设备内部零件之间说好的“暗号”和“修路方法”,确保数据能又快又稳地传过去。

常见接口定义(需结合实际):

D-PHY接口定义

D-PHY是MIP!总线的物理层,用于在发送和接收设备之间传输数据。D-PHY总共有19根线,其中16根是数据传输线。下面是D-PHY接口中的引脚定义:

CLOCK:时钟信号,用于同步序列化和反序列化的数据

HS-Data0~15:高速数据线,可传输16位高速数据。正常情况下,只使用其中几条高速数据线。

LP-Data0~2:低功耗数据线,可传输1至3位的低速数据。

Lane 0~3:高速和低速数据线的组合。每组包括1条高速数据线和1至3条低速数据线。

ULPS CLK: Ultra Low Power State 时钟信号,用于设备进入低功耗状态

ULPS DATA: Ultra Low Power State 数据线

C-PHY接口定义

C-PHY是MIPI总线的新一代接口,支持更高的数据传输速率和更节能的设计。与D-PHY不同,C-PHY共有22个引脚,其中4个是时钟引1脚。下面是C-PHY接口中的引脚定义:

CLKIN:输入时钟,用于指定时序。通常采用LVCMOs电平.

CLKOUT: 输出时钟,用于与接收设备对齐数据:

Lane 0+:高速串行数据线

Lane 0-:高速串行数据线

Lane 1+:高速串行数据线

Lane 1-:高速串行数据线

Lane 2+:高速串行数据线

Lane 2-:高速串行数据线

Lane 3+:高速串行数据线

Lane 3-:高速串行数据线

ANA OUTP: 表示输出端为模拟信号

ANA OUTN: 表示输出端为模拟信号

ANA INP: 表示输入端为模拟信号

ANA INN:表示输入端为模拟信号

REG OUT:用于根据硬件内存检查中的读或写信号进行寄存器读取/写入。

REG IN: 用于根据硬件内存检查中的读或写信号进行寄存器读取/写入。

LPDTI:低速数据传输接口

LPDTI 1P5V: 低速数据传输接口1.5V电压级别

LPDTI GND: 地线

ULPMIPI CLK: 用于设备进入Ultra Low Power Mode的时钟信号

ULPMIPI DATA: 用于设备进入Uitra Low Power Mode的数据信号

第二阶段:MIPI修了哪些“路”?—— 核心“高速公路”类型

MIPI联盟定义了好几种“路”,但最核心、你最需要知道的是两条:

2.1. CSI(摄像头串行接口)—— “原料进口高速路”

干什么用:专门负责把摄像头拍到的图像数据,高速运送到处理器(CPU/SoC)进行处理。

比喻:就像一条从图像工厂(摄像头)直通中央处理中心(处理器) 的专用货运高速。

2.2. DSI(显示屏串行接口)—— “成品出口高速路”

干什么用:专门负责把处理器处理好、要显示的图像数据,高速运送到屏幕上显示出来。

比喻:就像一条从中央处理中心(处理器)直通展示窗口(屏幕) 的专用货运高速。

重要关系:

CSI/DSI是“运输规则”,规定了货怎么装、车怎么排队。

D-PHY/C-PHY是 “道路建设标准” ,规定了路用啥材料、路基多宽、限速多少。

通常,CSI/DSI这套运输规则,是跑在D-PHY这条路上的。

第三阶段:“路”是怎么修的?—— D-PHY物理层详解(核心!)

这是理解MIPI硬件设计的关键。D-PHY就是那条“路”的具体修法。

3.1. 路的核心结构:“车道”

一条MIPI“高速公路”由两种车道组成:

1条时钟车道:这不是运货的,而是统一节奏的“发令员”。它持续发出“滴答、滴答”的节拍,确保所有数据货车步调一致,不会撞车或掉队。

1~4条数据车道:这才是真正运货的主车道。车道越多,同一时间能跑的货车就越多,运货能力(带宽)就越强。

普通720P/1080P视频,1-2条车道就够。

4K高清视频,可能需要3-4条车道。

3.2.路的两种工作模式:“飙车模式”和“溜车模式”

为了省电,这条路设计得非常聪明,有两种状态:

高速模式:

状态:货车挂最高档位飙车!速度极快(每条车道每秒能跑几亿到几十亿比特)。

运什么:只运大量的图像数据(一帧帧的画面)。

信号特点:使用差分信号(每车道两根线,信号互为反相)。这就像两个人抬一个担子,中间的重物(数据)很稳,旁边的颠簸(外界干扰)影响不到它,所以抗干扰能力强,能开快车。

低功耗模式:

状态:货车挂空档,靠惯性溜车。速度很慢,但极其省油(省电)。

运什么:运简单的控制指令,比如:“摄像头,开始拍!”“屏幕,休眠!”

信号特点:使用简单的单端信号,电压摆幅大,但速度慢,功耗极低。

关键在于无缝切换:当需要传一大包图像时,瞬间切换到“飙车模式”高速传完;传完后立刻切回“溜车模式”待机省电。这个切换速度极快,你根本感觉不到。

3.3. 带宽怎么算?(能运多少货?)

公式很简单:总运力 = 单车道的速度 × 车道数量

举例:一条车道每秒能运1.5G比特的货,我用2条车道,总运力就是 3.0 Gbps。这决定了你的摄像头最高能支持多少分辨率、多少帧率的视频。

第四阶段:怎么用这条路?—— 以摄像头为例

现在,你作为手机的设计师,要让一个摄像头通过MIPI CSI接口把图传给处理器。

4.1. 硬件连接(把工厂和高速路口连起来)

把摄像头的MIPI数据线、时钟线,正确连接到处理器的MIPI接收引脚上。

同时,还要用I2C这两根“电话线”连接起来,用来发控制指令(“开始拍”、“调亮度”)。

4.2.软件配置(制定运输合同)

通常需要查看设备树(硬件配置文件)

4.3. 工作流程

待机:大家都处在“溜车模式”(低功耗),处理器通过“电话线”(I2C)告诉摄像头:“兄弟,用2条车道,按RAW10格式打包货,准备发1080P的图”。

发货:摄像头收到指令。先切到“飙车模式”,发出一包“帧起始”标志(短数据包),然后开始疯狂发送图像数据包(长数据包)。

运输:数据在MIPI“高速路”上飞驰。

收货:处理器根据时钟车道的节拍,稳稳地收下所有数据包,看到“帧结束”标志就知道这一批货收完了。

待命:双方瞬间切回“溜车模式”省电,等待下一次发货指令。

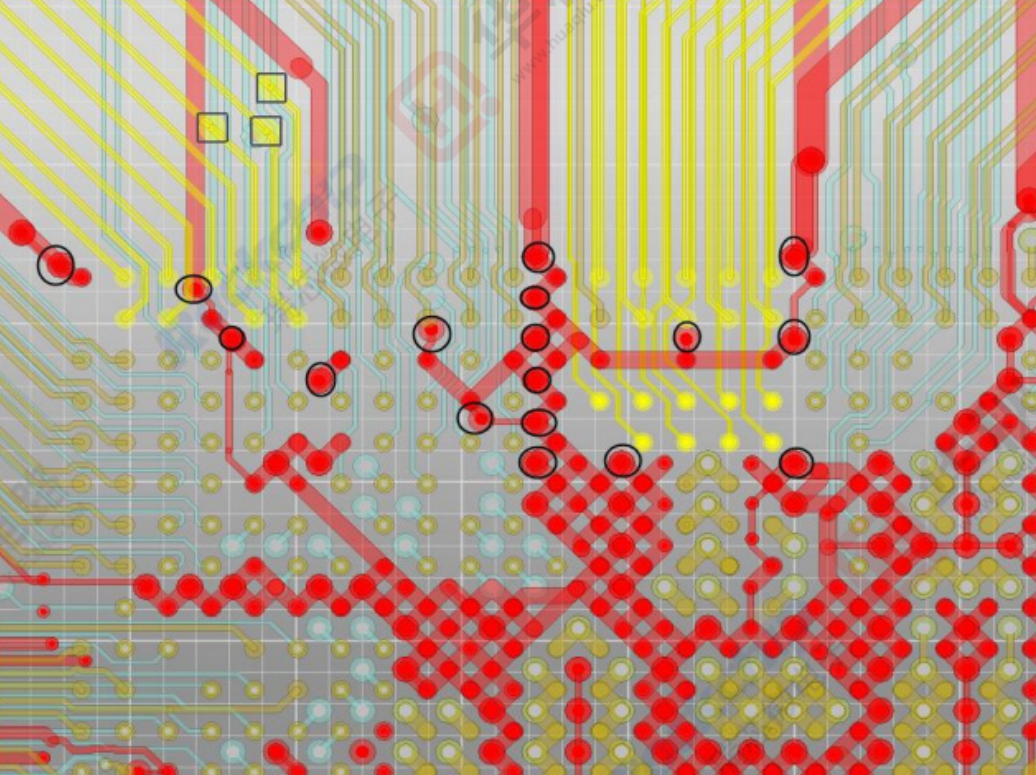

第五阶段:PCB设计规范

5.1、MIPI接口的PCB布局要求

1、远离干扰源,防止其他信号干扰到传输速率以及信号的传输质量,

2、所有的显示接口(不管是采用的是接口或者是FPC的形式的)尽量靠在板边放置,方便拔插

3、 主芯片与显示接口的位置不要放置的太远,尽量缩短走线的距离,走线按照高速信号走线。

4、如PCB有结构上要求,要严格按照结构放置。

5.2、MIPI接口的PCB布线要求

1、 参考层:为了抑制电磁辐射,MIPI的差分线尽量靠近GND平面的走线层来走线,保证走线不要跨分割,否则会造成差分线阻抗的不连续性和增加外部噪声对差分线的影响,如果是走在表层,尽量包地处理或者拉大跟其它信号的间距。

2、包地:MIPI走线可以整组包地,GND包地线每隔150mil打一个GND过孔。如果空间准许,可以单组包地。

3、 MIPI信号的差分线尽可能的减少过孔换层,过孔会造成线路阻抗的不连续,如果需要打孔换层来走线,保证差分过孔的一致性,以及在换孔位置就近安排一个回流地过孔,以用于信号回流

4、原理干扰:MIPI信号线应远离其它高速信号(如并行数据线,时钟线等),对开开关电源这一类的干扰源更应远离。

MIPI-CPHY接口的PCB设计布线注意事项:

|

参数 |

要求 |

|

走线阻抗 |

差分100ohm +10%(优先选择 100 欧目标阻抗,如果叠层无法满足100欧目标阻抗, 至少保证阻抗满足 95ohm ±10%。) |

|

差分对内时延差 |

<6mi1 |

|

时钟与数据之间等长 |

<12mil |

|

走线长度 |

<6 inches |

|

各信号所允许过孔数量 |

建议不超过4个 |

|

差分对间间距 |

建议大于等于4倍 MIPI线宽,3至少要 3倍 MPI线宽 |

|

MIE 与其它信号间距 |

建议大于等于4倍 MIPI线宽,至少要3倍 MIPI线宽 |

MIPI-DPHY接口的PCB设计布线注意事项:

|

参数 |

要求 |

|

走线阻抗 |

单端50ohm±10% |

|

组内(TRIO_A\TRIO_B\TRIO_C)最大时延差 |

<6mil |

|

组间(TRIO0\TRIO1\TRIO2)等长要求 |

<100mil |

|

走线长度 |

<5 inches |

|

各信号所允许过孔数量 |

建议不超过2个 |

|

对间间距 |

建议大于等于4倍 MIPI线宽 |

|

MIPI与其它信号间距 |

建议大于等于4倍 MIPI线宽 |

建议在 BGA 区域的以下位置加地通孔

给小白的学习总结

建立模型:MIPI是设备内部的高速数据运输系统,核心是运图像和视频。

记住两条路:CSI(运进摄像头数据),DSI(运出显示数据)。

理解路的结构:D-PHY是路,有时钟道+数据道,能在“飙车模式” 和 “溜车模式” 间智能切换,实现高速且省电。

明白核心:车道越多、单车道速度越快,总带宽就越高,能支持的分辨率和帧率也越高。

硬件是关键:作为设计者,重中之重是把PCB上的MIPI差分线画好——等长、等距、阻抗对、走线短。

更多推荐

已为社区贡献12条内容

已为社区贡献12条内容

所有评论(0)