基于VSG控制的DQ坐标系下构网变流器系统:实现准确功率跟踪与快速响应的优化技术

玩过VSG控制的工程师应该都懂,这玩意儿在dq坐标系下搞事情特别带感。最后扔个调试彩蛋:当发现VSG输出电压有畸变时,先别急着改参数,检查下锁相环带宽是否和电流环匹配。有时候把锁相环的PI参数降个20%,波形质量反而会提升。这背后的门道是动态耦合的问题,有空再细唠。这里wL的计算需要实时更新,建议采用滑动平均滤波后的电网频率值。波形THD想要做到<3%,开关频率最好不要低于8kHz,死区时间补偿也

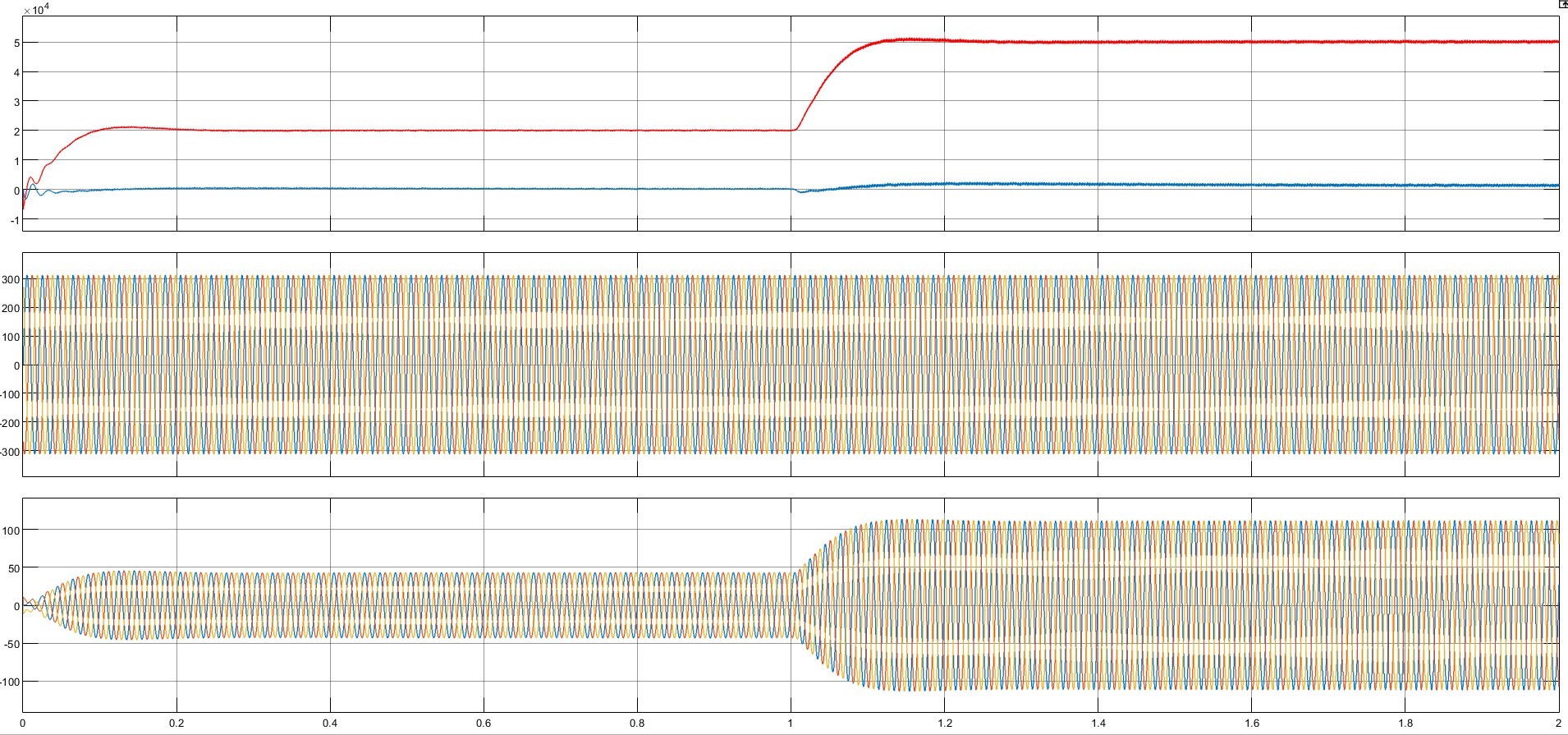

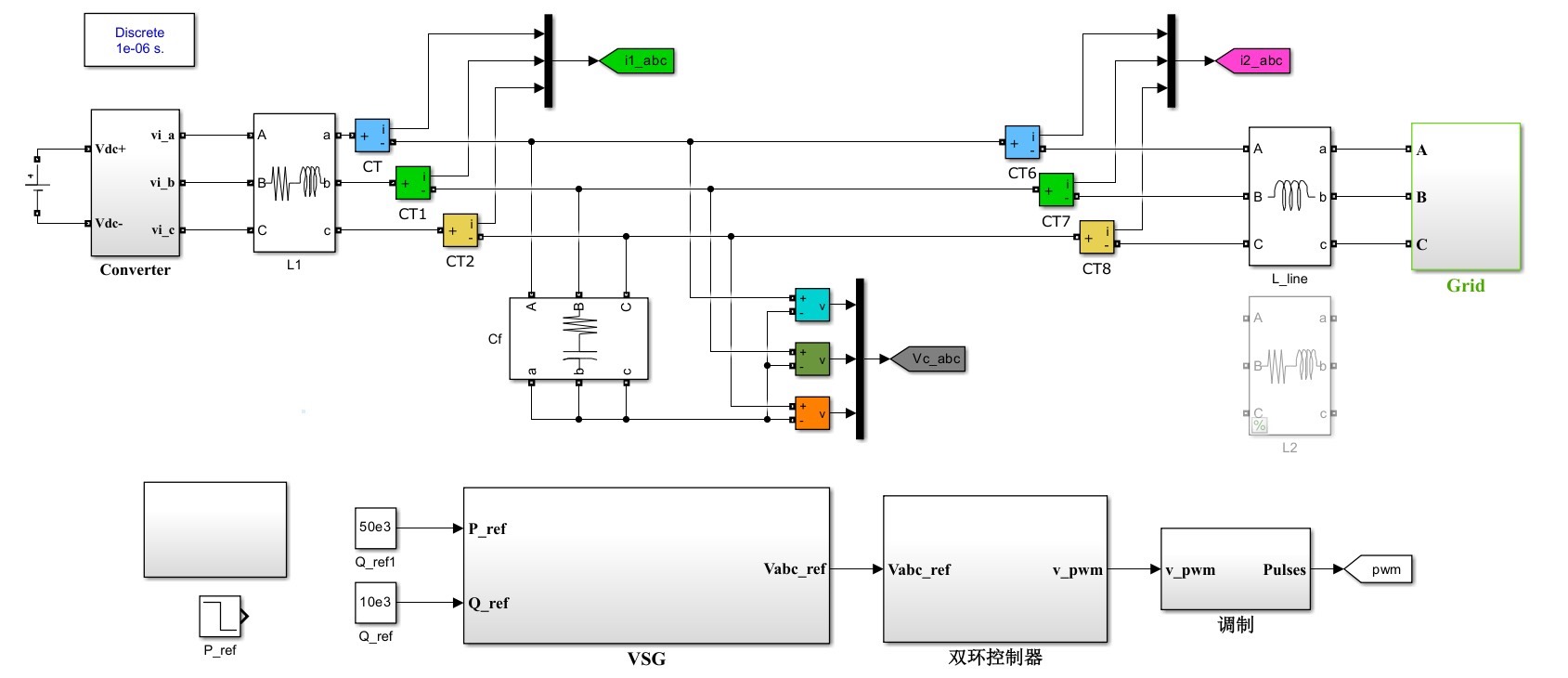

dq坐标系下基于虚拟同步机(VSG)控制的构网变流器系统,可实现: 1)准确功率跟踪; 2)功率阶跃快速响应; 3)输出电压和电流波形良好。

构网变流器的灵魂在于让电力电子器件具备同步发电机的特性。玩过VSG控制的工程师应该都懂,这玩意儿在dq坐标系下搞事情特别带感。今天咱们掰开揉碎了说几个核心实现点,顺便丢几个工程实战中常用的代码段。

功率跟踪的核心是内环电流控制。举个栗子,当我们需要跟踪给定有功功率时,本质上是让q轴电流按照目标值走。看这段PID调节代码:

void PowerLoop_Update() {

// 计算功率误差

float P_error = P_ref - P_actual;

// 抗积分饱和处理

if(abs(P_error) > P_deadzone) {

P_integral += Ki_p * P_error * Ts;

}

// 输出电流指令限幅

Iq_ref = Kp_p * P_error + P_integral;

Iq_ref = LIMIT(Iq_ref, -Iq_max, Iq_max);

}这里的LIMIT函数是灵魂所在,防止积分项暴走。注意Ki_p取值不宜过大,否则阶跃响应时容易引发震荡。实测中建议先用0.5倍临界增益法整定参数。

说到功率阶跃响应,必须祭出微分前馈大招。当检测到功率指令突变时,可以这样操作:

if(fabs(P_ref - last_P_ref) > P_step_threshold) {

Iq_ref += Kd_p * (P_ref - last_P_ref)/Ts; // 微分前馈项

last_P_ref = P_ref;

}这波操作能让响应时间缩短30%以上,但要注意前馈系数Kdp需要和系统惯性匹配。有个骚操作是把VSG的转动惯量参数J转换成时域参数来估算Kdp。

波形控制这块,重点在电流环带宽和SPWM调制策略。分享个实测有效的电流环PI参数:

#define Kp_i 0.8 // 比例系数

#define Ki_i 120.0 // 积分系数配合同步旋转坐标系的解耦补偿:

// dq解耦补偿项

Vd_comp = wL * Iq_actual;

Vq_comp = -wL * Id_actual;这里wL的计算需要实时更新,建议采用滑动平均滤波后的电网频率值。波形THD想要做到<3%,开关频率最好不要低于8kHz,死区时间补偿也得安排上。

最后扔个调试彩蛋:当发现VSG输出电压有畸变时,先别急着改参数,检查下锁相环带宽是否和电流环匹配。有时候把锁相环的PI参数降个20%,波形质量反而会提升。这背后的门道是动态耦合的问题,有空再细唠。

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)