将Altium Designer 25.7.1 原理图网表导入到 Allegro X Advanced Package Designer 23.1 的方法

本文介绍了将Altium Designer原理图网表导入Allegro X Advanced Package Designer的方法。首先需要将Altium原理图保存为ASCII格式,再通过Allegro X Design Entry CIS导入并转换为DNS格式。导入时需注意添加OFF PAGE CONNECTOR连接不同页面的同名网络。然后生成包含三个数据文件的网表,最后在Allegro X

将Altium Designer 原理图网表导入到 Allegro X Advanced Package Designer 23.1 的方法

Altium Designer 25.7.1 原理图保存为ASCII格式

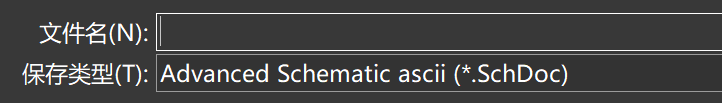

Altium Designer 默认情况下会将原理图保存成二进制格式。为了能够被Allegro X Design Entry识别,需要将原理图工程中的每个*.schdoc文件保存为ASCII格式,保存时保存类型选择如下图所示:

二进制文件与ASCII两种文件的区别是:二进制文件用记事本打开后是乱码,ASCII文件是文本文件,用记事本打开后是字符串。

Allegro X Design Entry CIS 导入原理图

在Allegro X Design Entry CIS 中选择File - Import - Altium Schematic Translator, 如下图所示:

PrjPCB File 选择Altium Designer中的原理图工程文件 *.PrjPCB, 生成的Allegro

导入原理图后,生成DNS格式的原理图工程*.DNS默认保存在./out/文件夹中。

ALLGERO CIS的原理图工程中不同页上的同名网络需要使用元件OFF PAGE CONNECTOR 才能够连接在一起,这一点与ALTIUM DESIGNER不同,因此,需要在每一页上添加元件OFF PAGE CONNECTOR,将各个页面的同名网络进行连接。

ALLEGRO CIS页面上的Online DRCs可以在线检测原理图上的问题,并给出错误和警告。给出的警告也要留意,如经常会提示:网络名只有一个引脚连接的警告,这种警告通常是由于未添加OFF PAGE CONNECTOR元件造成的。

ALLEGRO X CIS下生成工程的网表

在选中*.DSN的情况下,TOOLS - CREATE NETLIST, 创建工程的网表,

创建工程网表默认存储在当前目录下的allegro目录下,包括三个文件:

pstxnet.dat, pstxprt.dat, pstchip.dat.

ALLEGRO X ADP下导入网表

选择网表的目录allegro, 点击import, 就可以将原理图网表导入PCB.

ALLEGRO X ADP下对PCB的设计的检查

采用Display - Status 检查PCB设计的正确性:

更多推荐

已为社区贡献14条内容

已为社区贡献14条内容

所有评论(0)