HDI电路板的阶数

摘要:HDI电路板阶数由增层次数和激光钻孔流程决定,一阶(1+N+1结构)适用于消费电子,二阶(2+N+2)支持跨层连接用于5G设备,三阶及以上(3+N+3)实现任意层互联,用于高端智能手机和军工设备。阶数越高,工艺越复杂(如多次压合、UV激光钻孔),线宽可达0.05mm,成本也显著增加。选择时需平衡性能(如BGA节距)与成本,高阶HDI需解决对准精度(±15μm)和散热等挑战。行业遵循IPC-2

·

HDI(高密度互连)电路板的阶数是衡量其结构复杂度和制造难度的核心指标,主要通过增层次数、激光钻孔次数及层间连接方式来划分。以下是结合行业标准与实际应用的详细解析:

盲埋孔的阶数由 孔穿透的介质层数量 决定,电路板阶数由板内所制作的最大盲埋孔阶数决定

一、阶数定义与划分规则

- 一阶HDI

- 结构:1+N+1(两侧各1次增层,中间为N层芯板)。

- 工艺:单次激光钻孔,盲孔仅连接表层与相邻内层(如L1-L2、L5-L6)。

- 层数:通常为4层(如1+2+1),也可扩展至6层(1+4+1)。

- 应用:消费电子(如智能手表、蓝牙耳机),支持0.5mm节距的BGA封装。

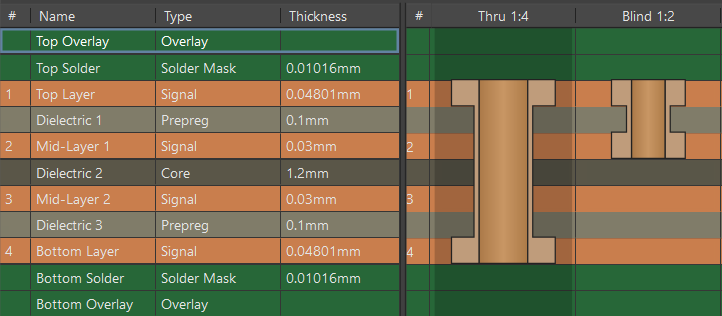

下图为四层一阶电路板

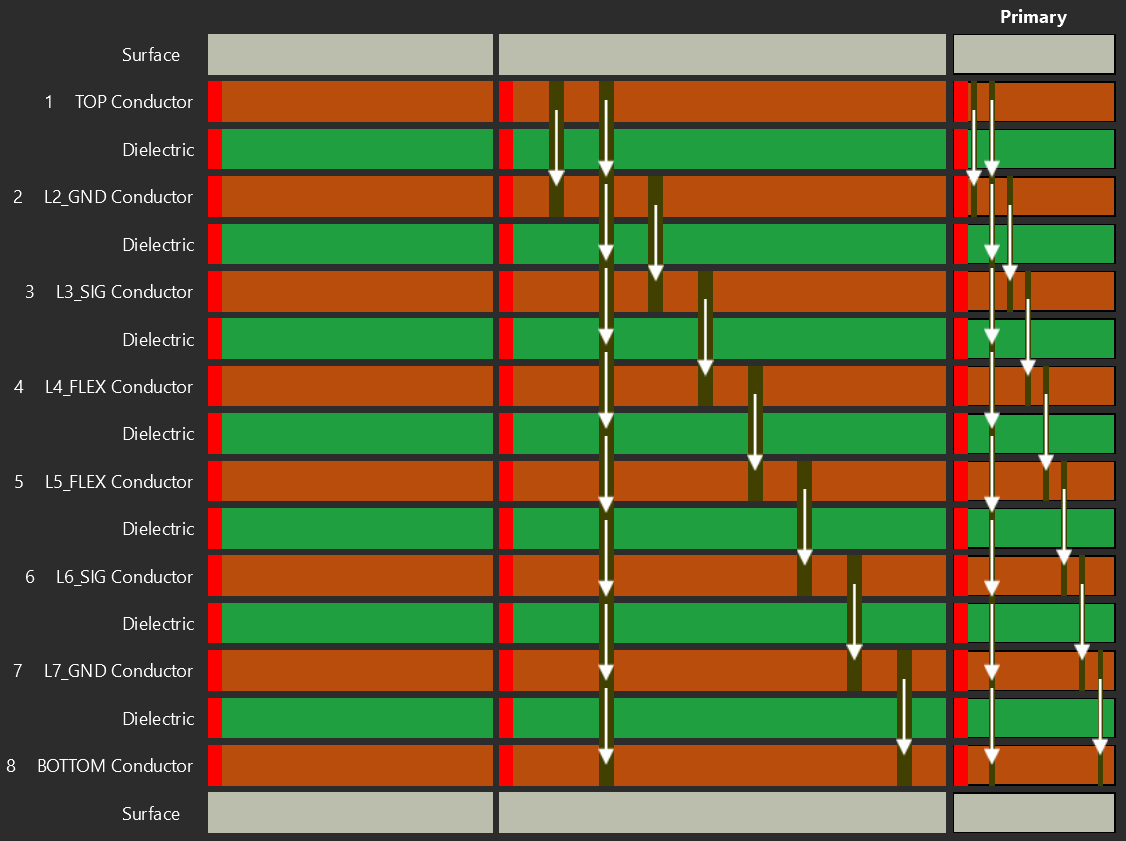

下图为一阶8层电路板

- 二阶HDI - 结构:2+N+2(两侧各2次增层)。

- 工艺:两次激光钻孔,可实现跨层连接(如L1-L3、L4-L6),分为错孔和叠孔两种类型:

- 错孔二阶:盲孔L1-L2与L2-L3错开,需通过内层导线连通;

- 叠孔二阶:盲孔L1-L2与L2-L3叠加,直接形成L1-L3的贯通。

- 层数:6层(2+2+2)或8层(2+4+2)。

- 应用:5G通信基站、服务器主板,支持0.4mm节距的BGA封装。

- 工艺:两次激光钻孔,可实现跨层连接(如L1-L3、L4-L6),分为错孔和叠孔两种类型:

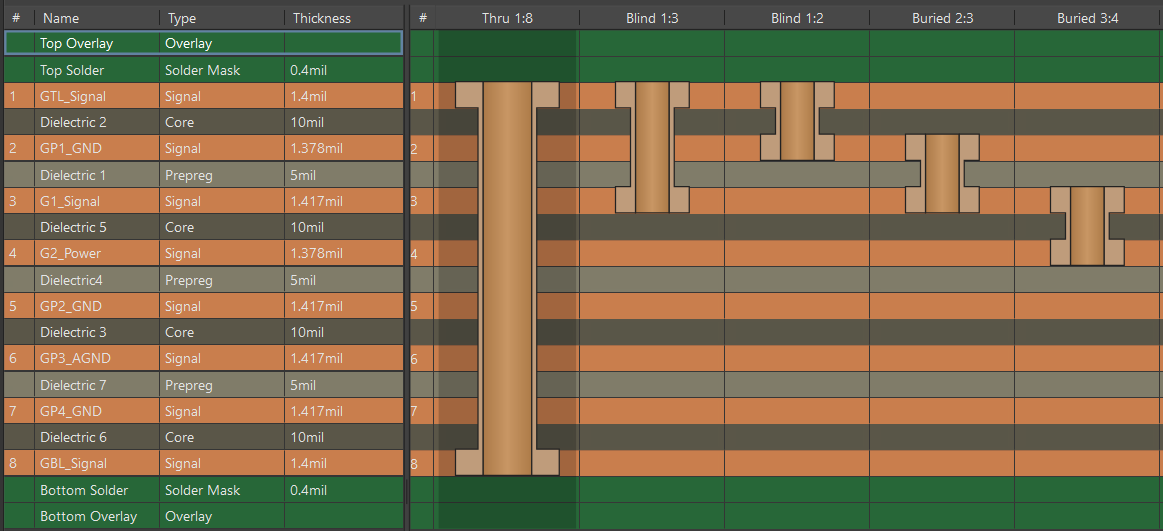

如图:以下电路板为8层2阶HDI电路板:

- 三阶及以上HDI

- 结构:3+N+3及更高(两侧各3次以上增层)。

- 工艺:多次激光钻孔与顺序层压,实现任意层互联(Anylayer HDI),四阶及以上需引入载板工艺(SLP)。

- 层数:8层以上(如3+4+3),最高可达30层。

- 应用:智能手机主板、军用雷达、卫星通信设备,支持0.3mm以下节距的FCBGA封装。

二、阶数与工艺参数的关系

-

层压次数

- 一阶:2次压合(芯板+外层);

- 二阶:3次压合(芯板+两次增层);

- 三阶:4次以上压合,需采用等离子蚀刻、电镀填孔等工艺。

-

激光钻孔技术

- 一阶:CO₂激光(孔径0.15-0.3mm);

- 二阶及以上:UV激光(孔径≤0.1mm),支持更高精度和深宽比(≤0.8:1)。

-

线宽/间距

- 一阶:线宽/间距≥0.1mm;

- 二阶:线宽/间距0.075-0.1mm;

- 三阶:线宽/间距≤0.05mm,布线密度可达120线/cm²。

三、典型阶数的结构示例

-

一阶HDI(4层板)

- 层叠:L1(信号)-L2(地)-L3(电源)-L4(信号);

- 连接:L1-L2、L3-L4盲孔(激光钻孔),L2-L3通孔(机械钻孔)。

-

二阶HDI(6层板)

- 层叠:L1(信号)-L2(地)-L3(信号)-L4(电源)-L5(地)-L6(信号);

- 连接:L1-L2、L5-L6盲孔(第一次激光钻孔),L2-L3、L4-L5盲孔(第二次激光钻孔),L3-L4埋孔(机械钻孔)。

-

三阶HDI(8层板)

- 层叠:L1(信号)-L2(地)-L3(信号)-L4(电源)-L5(地)-L6(信号)-L7(电源)-L8(信号);

- 连接:L1-L2、L7-L8盲孔,L2-L3、L6-L7盲孔,L3-L4、L5-L6埋孔,L4-L5通孔(机械钻孔)。

四、应用场景与阶数选择

| 阶数 | 层数范围 | 典型应用场景 | BGA节距 | 成本系数 |

|---|---|---|---|---|

| 一阶 | 4-6层 | 消费电子(智能手表、TWS耳机) | ≥0.5mm | 1.0 |

| 二阶 | 6-8层 | 通信基站、服务器、高端显卡 | 0.4-0.5mm | 1.3-1.5 |

| 三阶 | 8-12层 | 智能手机主板、汽车ADAS系统 | 0.3-0.4mm | 2.0-2.5 |

| 四阶及以上 | ≥10层 | 类载板(SLP)、军工航天设备 | ≤0.3mm | 3.0+ |

- 消费电子:优先选择一阶或二阶,平衡成本与密度需求;

- 高端通信:二阶或三阶,支持高速信号(如PCIe 5.0、DDR5);

- 军工航天:三阶及以上,需满足极端环境下的可靠性(如-55℃~125℃温度循环)。

五、行业标准与认证

-

IPC-2226

- 将HDI分为I至VI类,其中I类对应一阶,II类对应二阶,III类对应三阶及以上。

- 标准明确了微孔尺寸(≤0.15mm)、环宽(≤75μm)等关键参数。

-

可靠性测试

- 汽车电子:AEC-Q100认证(1000次温度循环);

- 5G通信:28GHz频段插损≤0.5dB/inch;

- 军工航天:IPC-6012 Class 3标准(100% X射线检测)。

六、技术趋势与挑战

-

任意层HDI(Anylayer)

- 支持盲孔直接连接任意层,消除埋孔限制,布线密度提升30%以上,适用于AI芯片封装。

-

类载板(SLP)

- 采用半加成法(mSAP)和超薄芯板(≤0.05mm),线宽/间距可降至0.025mm,用于高端智能手机(如iPhone主板)。

-

工艺难点

- 对准精度:层间错位需控制在±15μm以内,依赖X射线靶标定位;

- 散热设计:高阶HDI需嵌入铜基热沉或纳米陶瓷基板,降低热阻。

通过以上解析,可清晰理解HDI阶数的核心逻辑与工程应用,设计时需结合功能需求、成本预算及制造能力综合选型。

更多推荐

已为社区贡献14条内容

已为社区贡献14条内容

所有评论(0)