LVDS知识点汇总及电路 PCB设计

:每个基色(RGB)采用6位数据,共18位数据。。

LVDS(Low Voltage Differential Signaling)也称为低电压差分信号,由于采用差分的形式进行信号传输,所以传输速率能到几百Mbps,而且噪音和功耗都较低。

一:LVDS结构

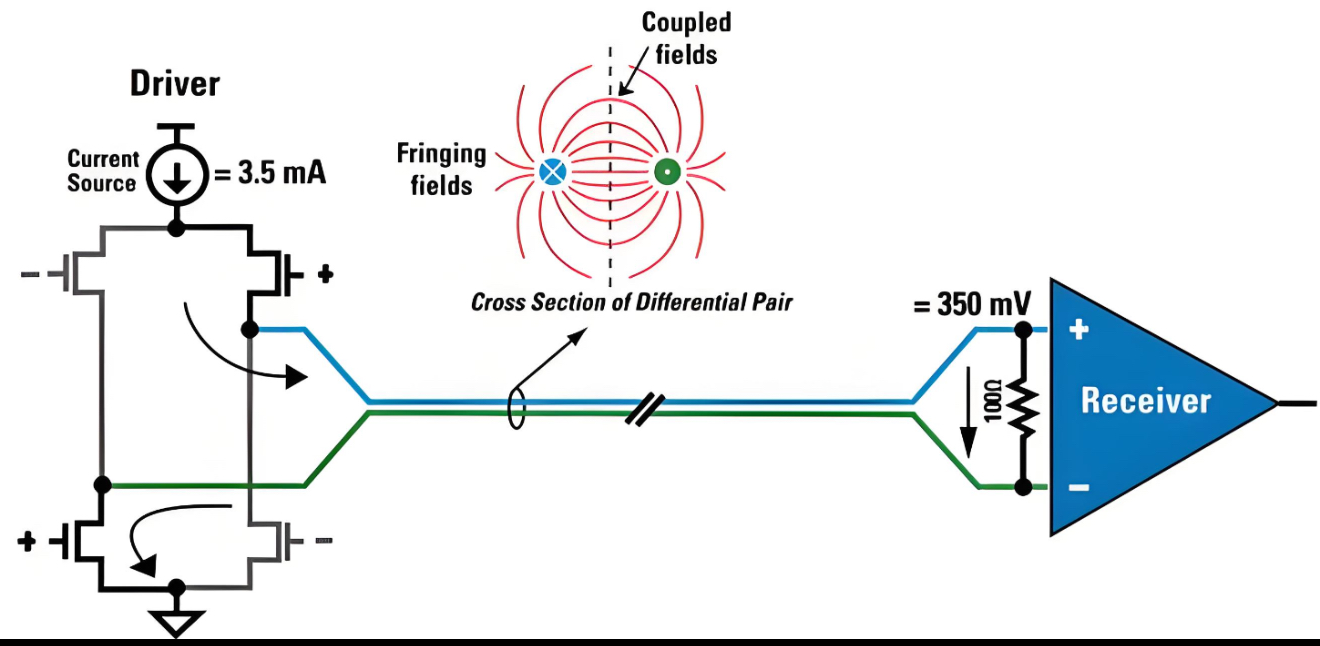

下图是LVDS的基本电路结构(图片来源于网络)

从基本结构中可以看得出来,LVDS是采用差分对的形式来传输信号,并通过驱动3.5mA的电流源来实现差分对之间350mV的低振幅的差动信号来传输数据。

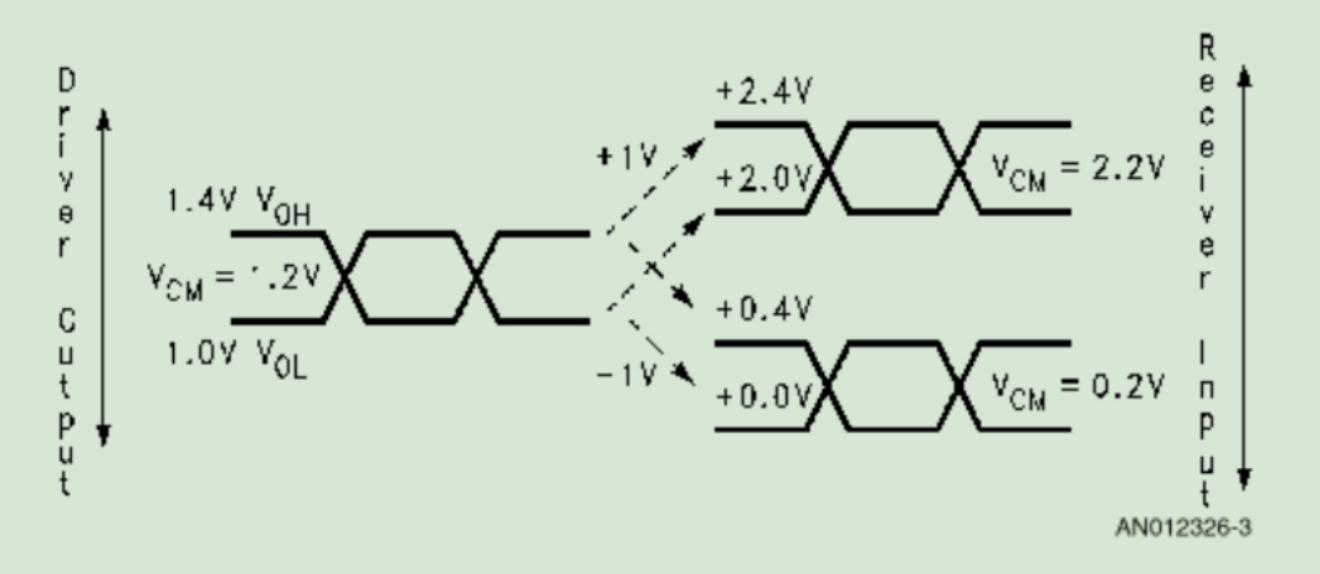

差分对之间的电平状态如下图所示:

二:LVDS常见接口分类及定义

LVDS接口中的单6、双6、单8、双8是描述液晶屏数据传输位数和通道类型的术语,具体区别如下:

1. 单6位(S6)

-

定义:每个基色(RGB)采用6位数据,共18位数据。

-

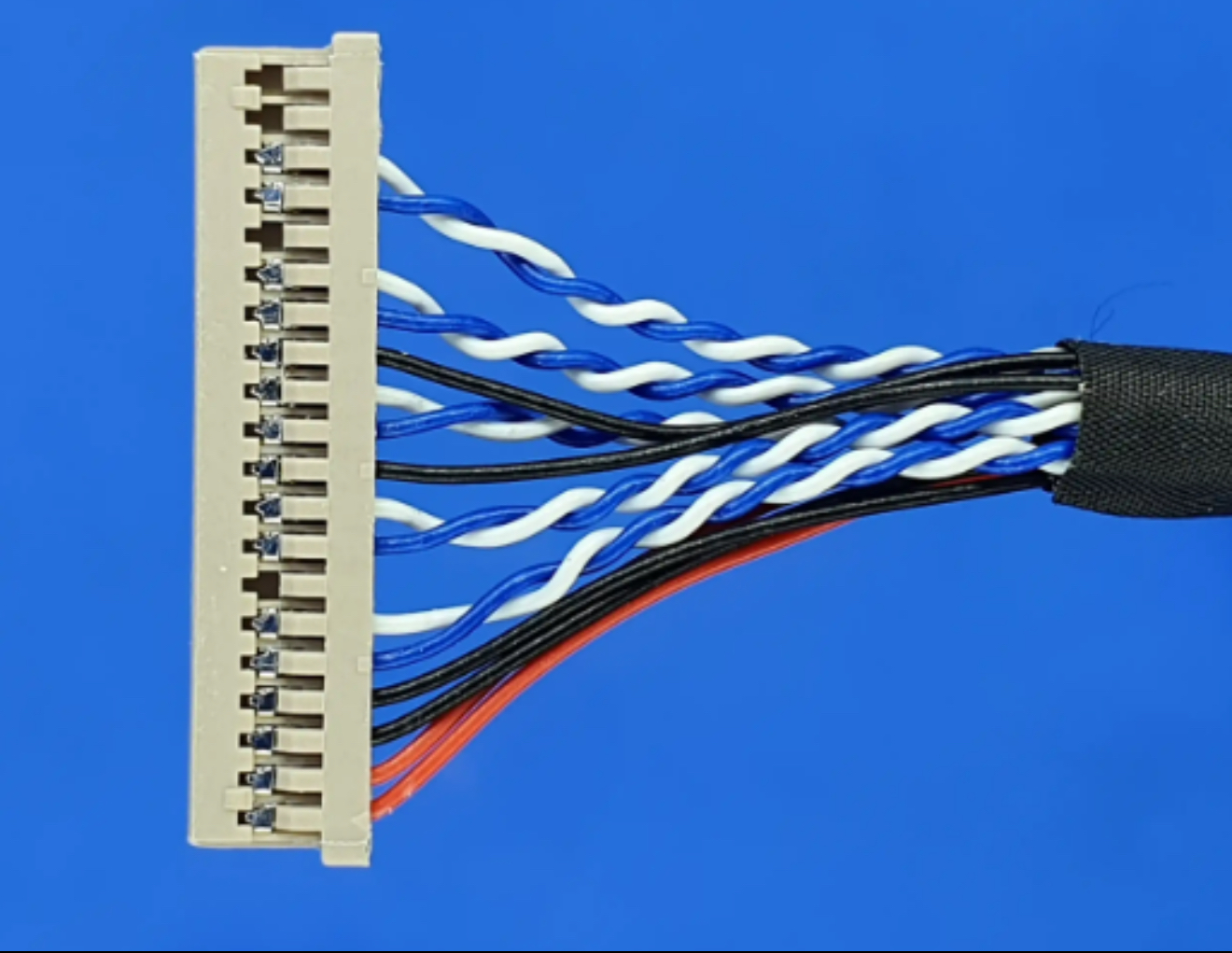

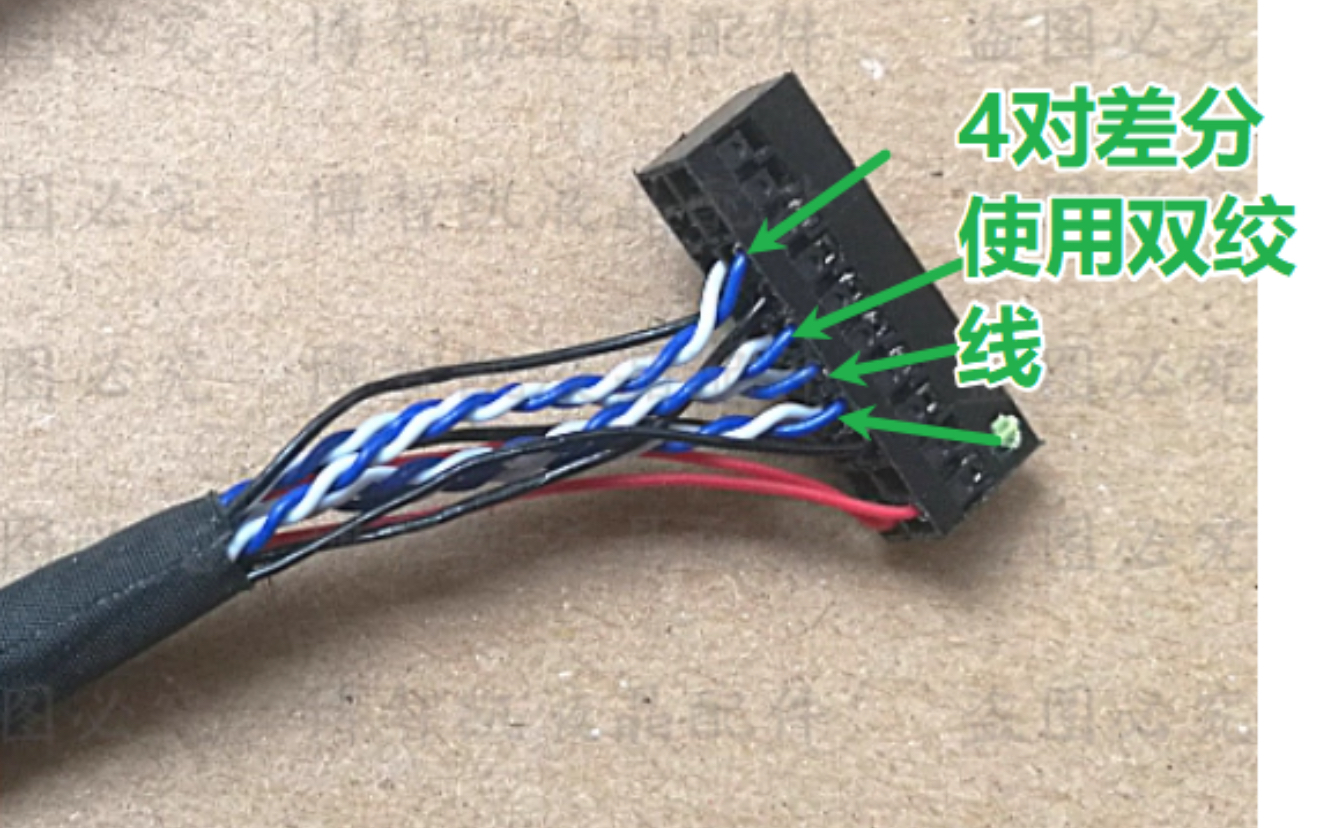

接口特征:4对差分信号线(3对数据+1对时钟)。

-

应用场景:低分辨率屏幕(如1366×768的笔记本屏)。

- 管脚分配:

-

1-2脚:电源(VCC)

-

3-4脚:地(GND)

-

5-6脚:R0差分信号(R0-、R0+)

-

7脚:地

-

8-9脚:R1差分信号(R1-、R1+)

-

10脚:地

-

11-12脚:R2差分信号(R2-、R2+)

-

13脚:地

-

14-15脚:时钟信号(CLK-、CLK+)

-

16-20脚:空脚

-

电阻值:每组差分信号线间电阻约120Ω。

-

2. 双6位(D6)

-

定义:双通道传输,每通道6位,共36位数据。

-

接口特征:8对差分信号线(6对数据+2对时钟)。

-

应用场景:中等分辨率屏幕(如1440×900的笔记本屏)。

- 管脚分配:

-

1-2脚:电源(VCC)

-

3-4脚:地(GND)

-

5-6脚:R0差分信号(R0-、R0+)

-

7-8脚:R1差分信号(R1-、R1+)

-

9-10脚:R2差分信号(R2-、R2+)

-

11-12脚:时钟信号(CLK-、CLK+)

-

13-14脚:RO1差分信号(RO1-、RO1+)

-

15-16脚:RO2差分信号(RO2-、RO2+)

-

17-18脚:RO3差分信号(RO3-、RO3+)

-

19-20脚:时钟信号(CLK1-、CLK1+)

-

-

电阻值:每组差分信号线间电阻约120Ω。

-

3. 单8位(S8)

-

定义:每个基色8位,共24位数据。

-

接口特征:5对差分信号线(4对数据+1对时钟)。

-

应用场景:标清屏(如1366×768的电视PC屏)。

- 管脚分配:

-

1-2脚:电源(VCC)

-

3-4脚:地(GND)

-

5-6脚:R0差分信号(R0-、R0+)

-

7脚:地

-

8-9脚:R1差分信号(R1-、R1+)

-

10脚:地

-

11-12脚:R2差分信号(R2-、R2+)

-

13脚:地

-

14-15脚:时钟信号(CLK-、CLK+)

-

16-17脚:R3差分信号(R3-、R3+)

-

-

电阻值:每组差分信号线间电阻约120Ω。

-

-

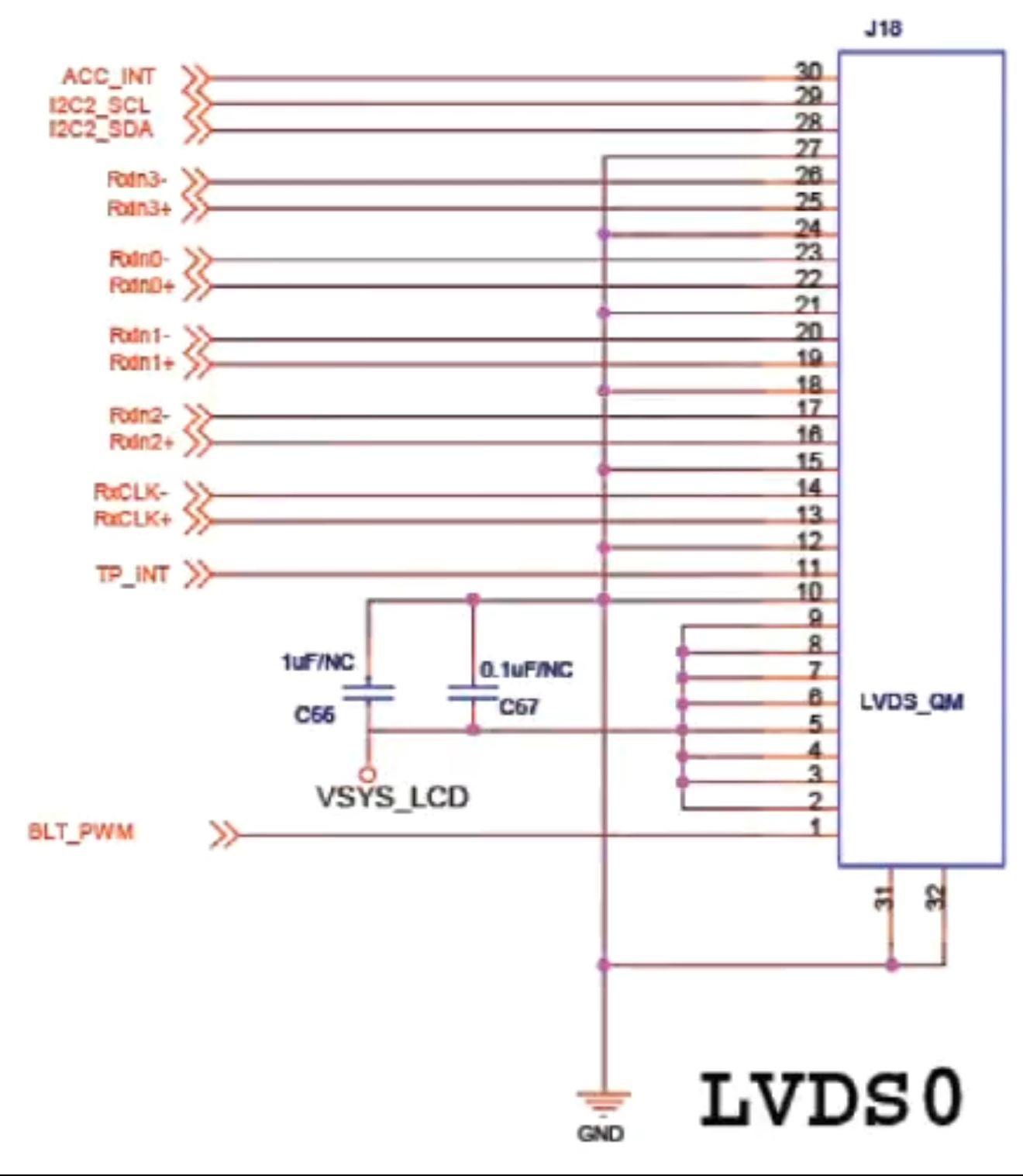

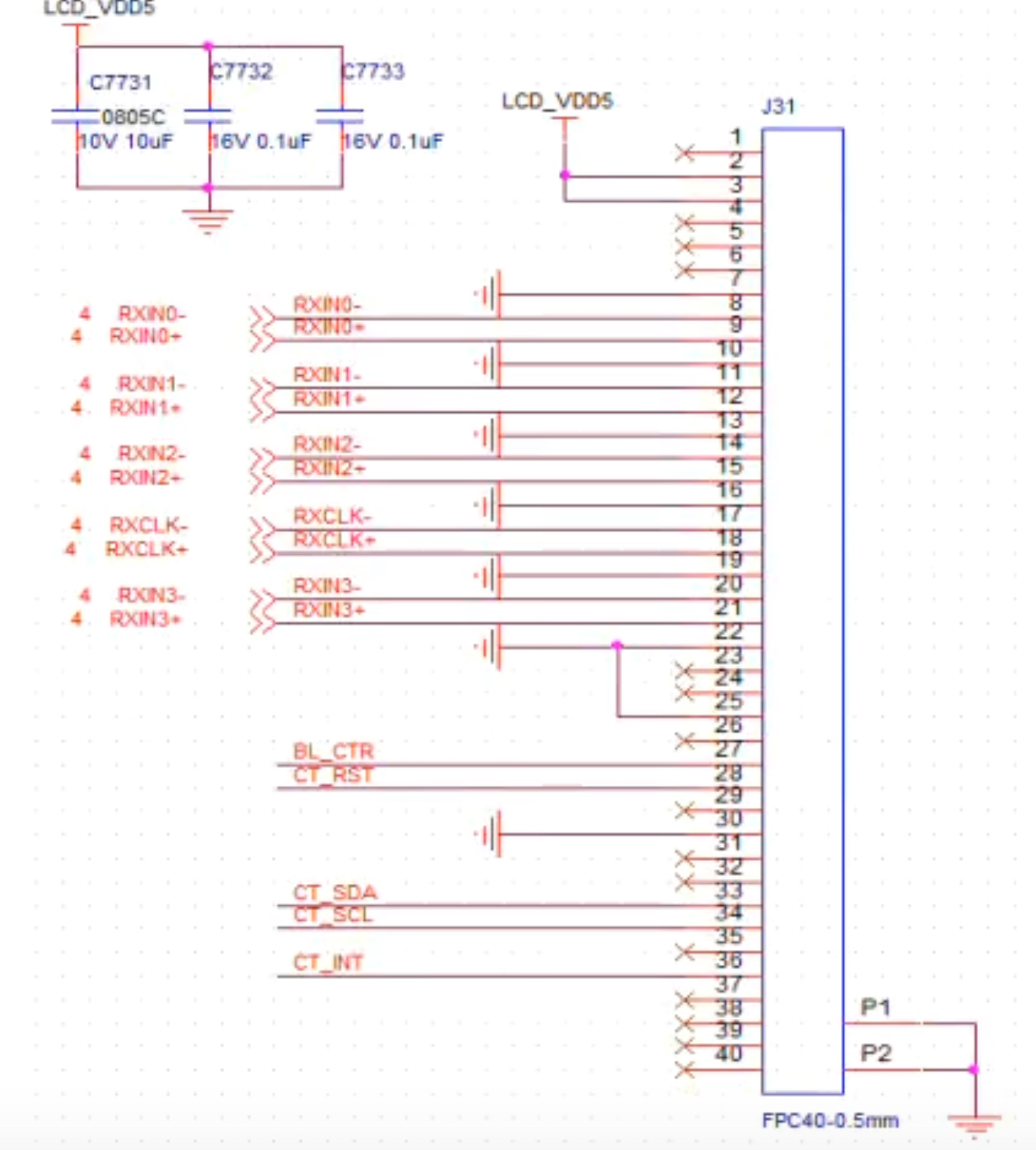

三:参考电路

电路其实也比较简单,如下图所示,仅供参考。

-

-

四:PCB布局走线建议

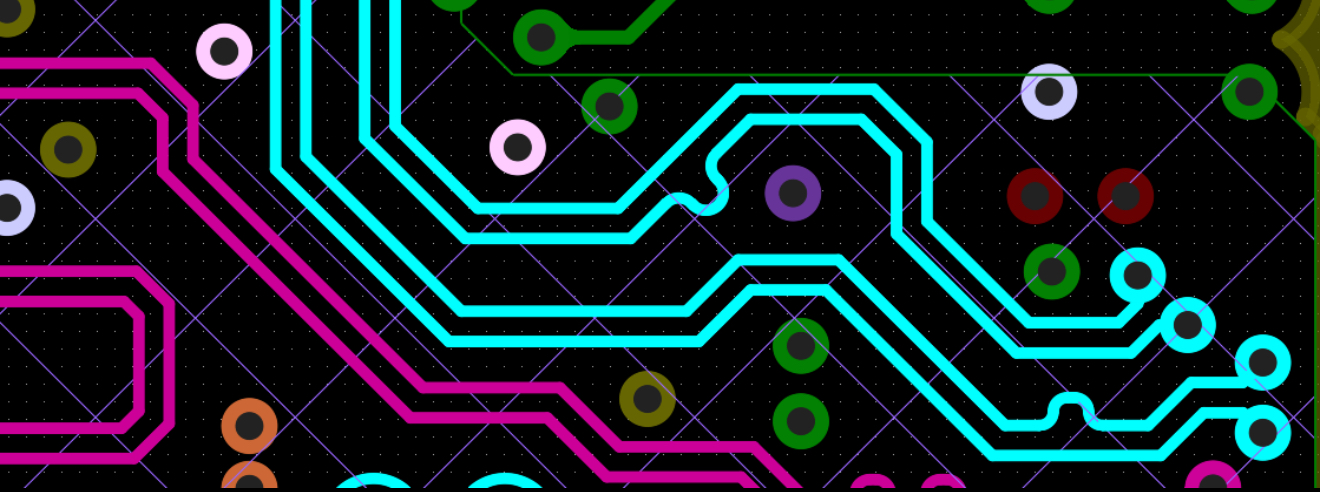

(1)LVDS差分对统一要做100Ω的阻抗匹配,差分对之间需保持等长。

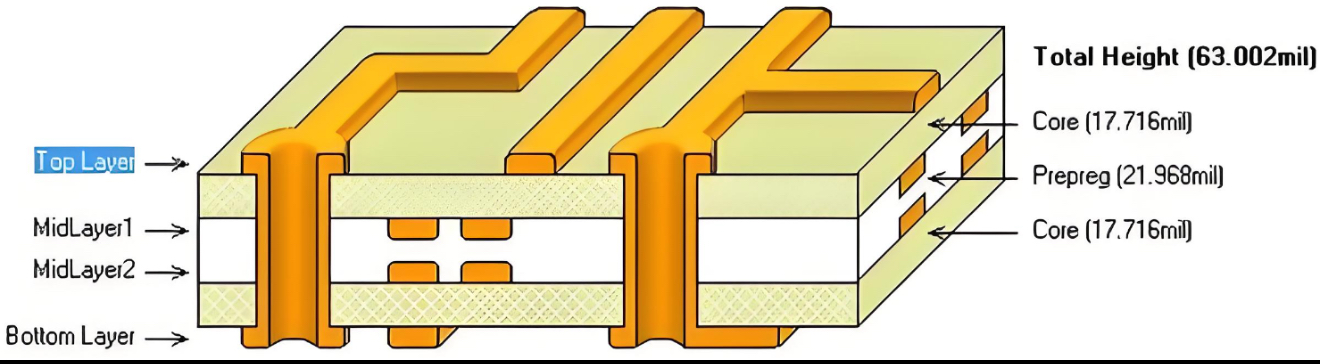

(2)由于差分对较多,建议常用4层以上的叠层设计。

(3)尽量保证完整的GND。

(4)电源滤波电容一定要靠近接口放置,而且电源必须先经过电容后才能给到LVDS接口。

(5)每组电源线需做加粗处理,避免出现电流瓶颈。

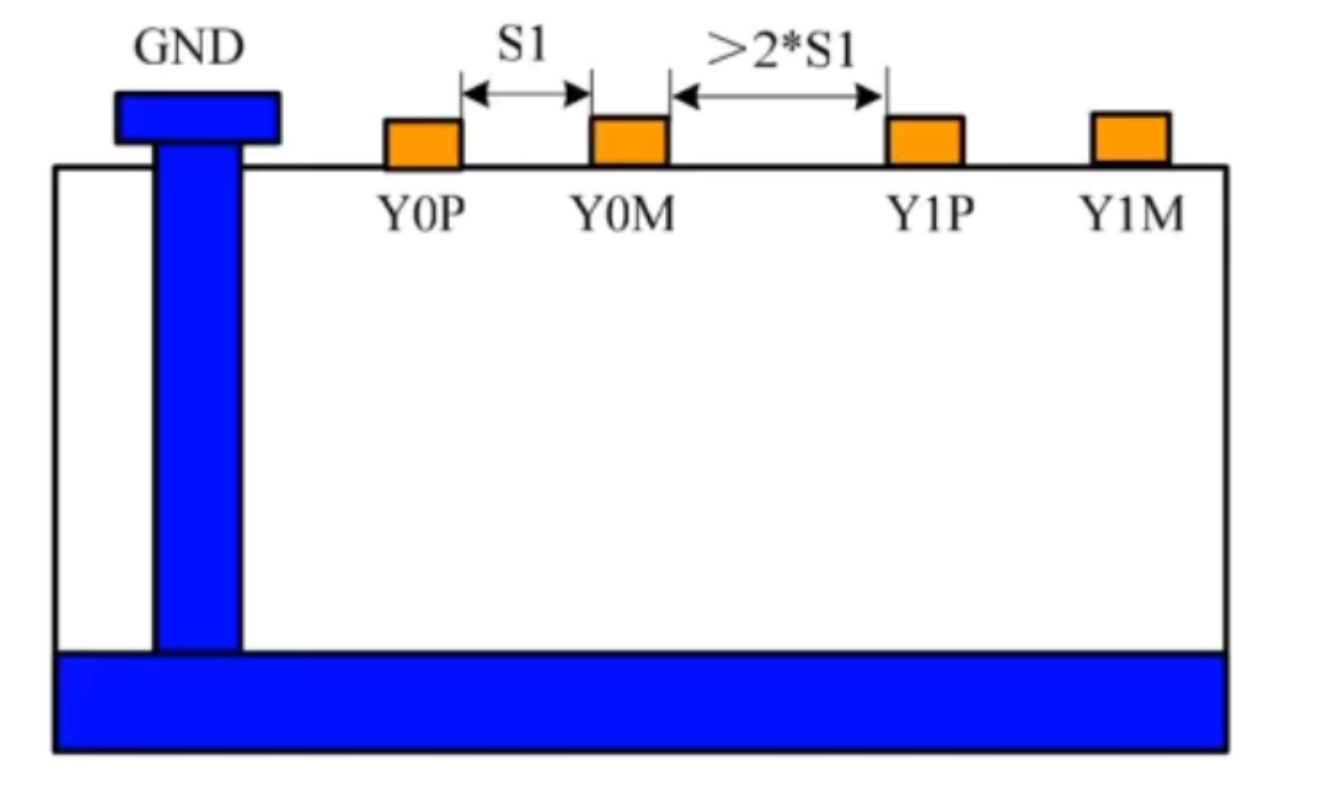

(6)LVDS各组差分对之间间隔至少大于2倍S1,如下图1所示:

(7)LVDS差分信号正负之间的距离S1尽量小(阻抗满足的前提下),如下图1所示:

(8)LVDS差分线尽可能少打孔,且走线避免90°弯角。

更多推荐

已为社区贡献16条内容

已为社区贡献16条内容

所有评论(0)